Les FPGA sont devenus célèbres ces dernières années car ils ont une multitude d’applications différentes et sont la logique programmable par excellence. Mais ceux-ci ont une contrepartie dans les CPLD, qui sont bien meilleurs pour certaines tâches et en même temps beaucoup moins chers. Que sont les CPLD et en quoi sont-ils différents des FPGA?

Pour comprendre ce que sont les CPLD, il faut d’abord comprendre l’évolution du matériel et, plus précisément, son intégration dans le temps. Il faut comprendre l’intégration comme l’union progressive de plusieurs appareils en un seul, profitant de la croissance du nombre d’appareils ou de transistors par zone.

Intégration des circuits au fil du temps

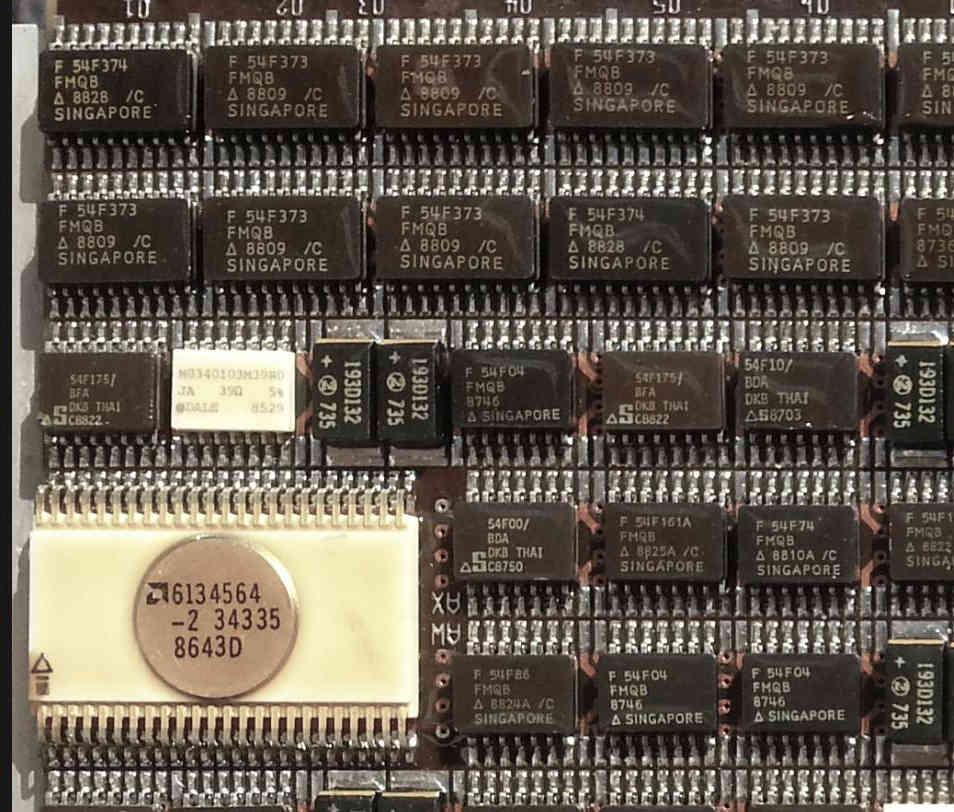

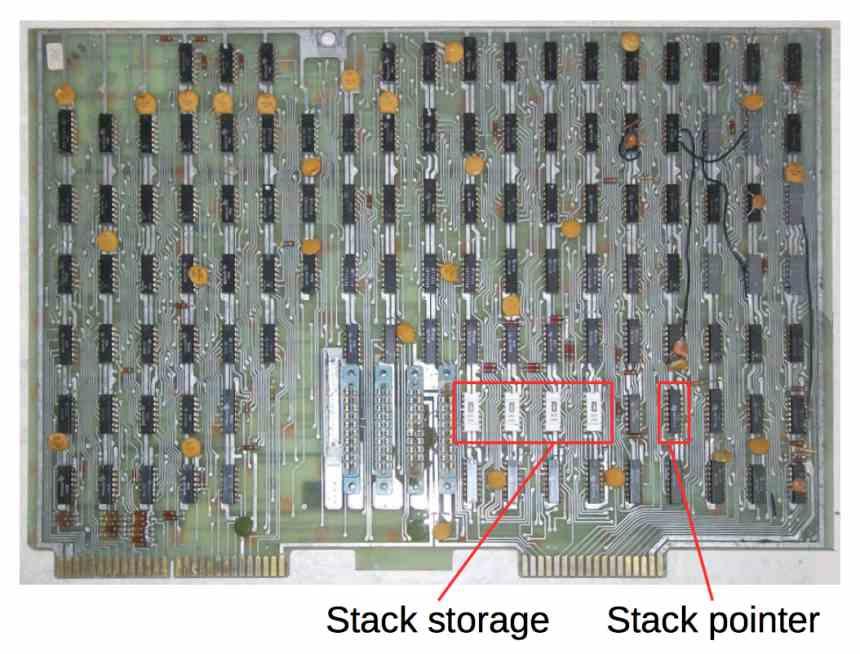

Les premiers ordinateurs étaient énormes, ils occupaient en fait plus d’une pièce dans de nombreux cas. La raison? Les architectures ont été construites avec une multitude de puces appelées TTL ou 7400 puces en l’honneur de la série Texas Instruments qui était la plus largement utilisée. En quoi consistaient-ils? Eh bien, dans les éléments de base pour la construction de circuits, qui pourraient aller de simples portes logiques à des systèmes séquentiels tels qu’un compteur binaire. Les conceptions ont été réalisées en connectant plusieurs de ces éléments pour obtenir une architecture spécifique.

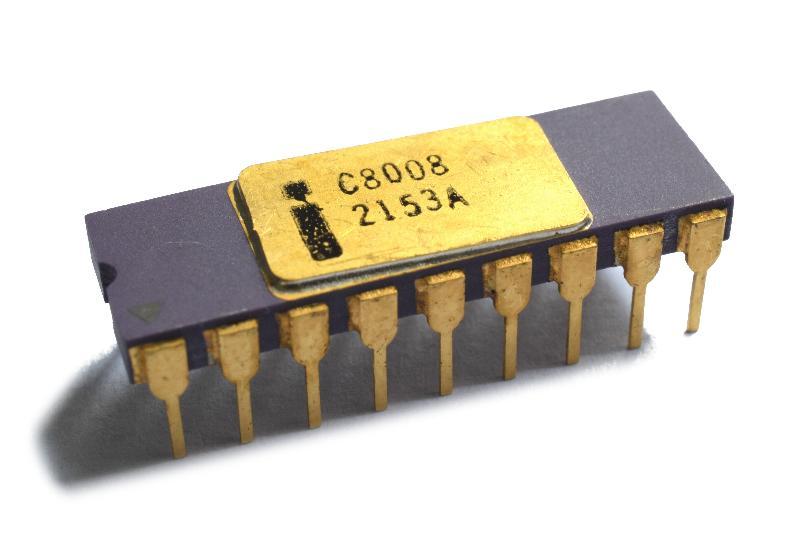

Mais l’avancement de ce que nous appelons la loi de Moore a apporté des densités de transistors plus élevées et la possibilité d’intégrer l’ensemble des circuits de plusieurs puces TTL sur une seule puce. À la fin des années 1960, les gens ont commencé à parler d’intégration à grande échelle, LSI, qui consistait à pouvoir intégrer des conceptions de 1000 à 10000 transistors sur une seule puce. Ce niveau d’échelle a permis à ce qui était autrefois un processeur composé de plusieurs puces différentes d’être unifié en une seule. De là sont venus les premiers processeurs pour ordinateurs personnels tels que l’Intel 8080 et son Zilog clone le Z80, le MOS 6502 et le Motorola 6800.

Mais comme les «mini» ordinateurs, aussi grands qu’un réfrigérateur ou même un placard, les nouveaux processeurs nécessitaient l’utilisation de circuits supplémentaires pour accélérer certaines tâches. Les premiers modèles ont commencé à utiliser des puces TTL pour certaines fonctions, mais au fil du temps, l’intégration de l’ensemble des circuits sur une seule puce a également été adoptée, comme cela s’était produit avec les processeurs. Cela a conduit à la création d’une logique programmable, avec laquelle les entreprises ont accéléré la construction des circuits qui accompagnaient le processeur.

Au début, il n’y avait pas de logique programmable, mais des ROMS

Techniquement, une ROM ne sert qu’à stocker des données qui ne peuvent être lues, mais des puces à fonction fixe peuvent être créées à l’aide de ROMS. Une puce à fonction fixe est une puce qui effectue toujours la même tâche sur des données d’entrée qui peuvent varier.

Comment implémentez-vous une fonction fixe dans une ROM? Simple, comme en RAM, il dispose d’un décodeur qui sélectionne une donnée de sortie. Il ne calcule vraiment rien, mais par exemple en sachant quel est le résultat de certaines opérations arithmétiques ou de certaines fonctions, celles-ci peuvent être encodées en sortie dans une ROM et accélérer certains calculs.

Le problème? Dans une ROM, nous ne pouvons pas coder le fonctionnement de la logique combinatoire et ni de la logique séquentielle, il est donc rapidement devenu nécessaire de créer un type de logique plus complexe pour l’intégration des circuits et avec elle la réduction des coûts.

PLA et PAL, les prédécesseurs du CPLD

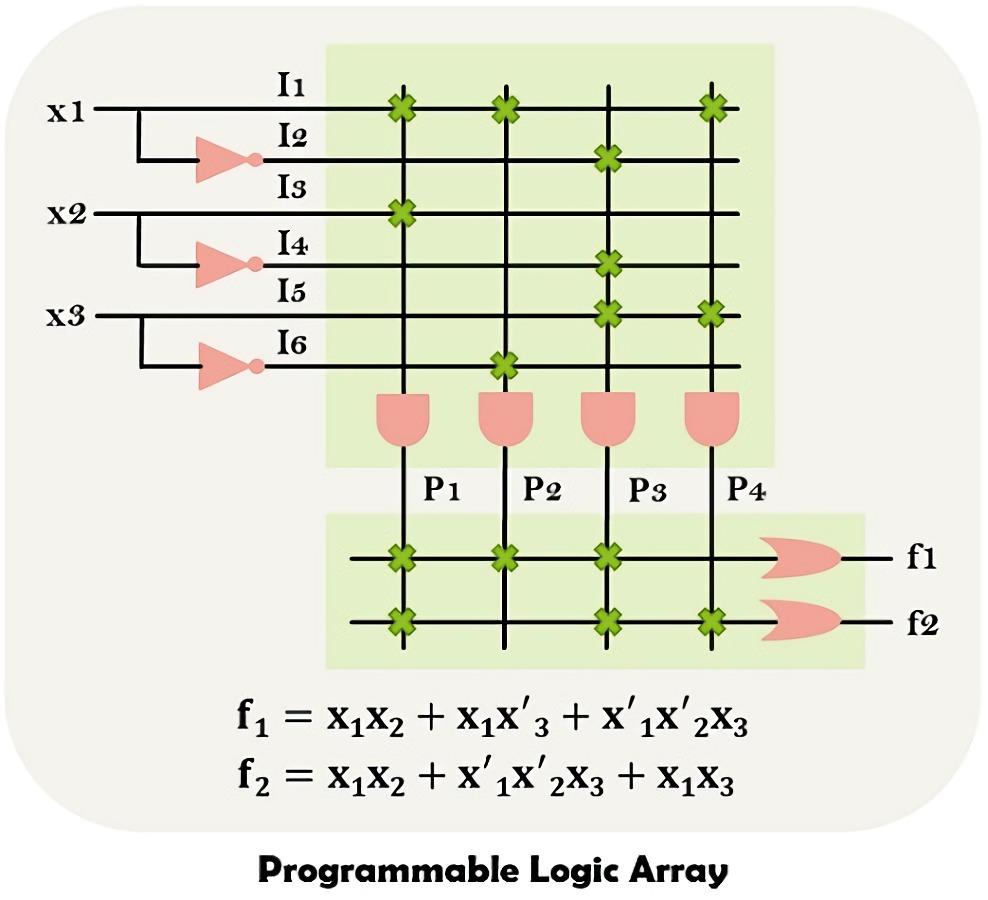

L’évolution vers l’utilisation des ROMS pour l’intégration de la fonction fixe a été la création des tableaux logiques programmables ou PLA, c’est un dispositif composé d’une série de portes logiques ET qui sont liées à une série de portes OU et chacune ayant l’un des leur un complémentaire de NE PAS inverser le résultat. Avec cela, vous pouvez créer des fonctions de logique combinatoire qui commencent par l’utilisation d’une porte ET ou NAND et se terminent par une porte OU. Les circuits PLA ont N entrées qui correspondent à N portes logiques ET et M sorties qui correspondent à des portes logiques OU.

Un autre type de logique programmable s’appelait PAL, Programmable Array Logic, où malgré la similitude du nom, ils ne fonctionnaient pas de la même manière puisque les portes OU étaient fixes et non programmables et étaient donc moins polyvalentes, mais beaucoup moins chères.

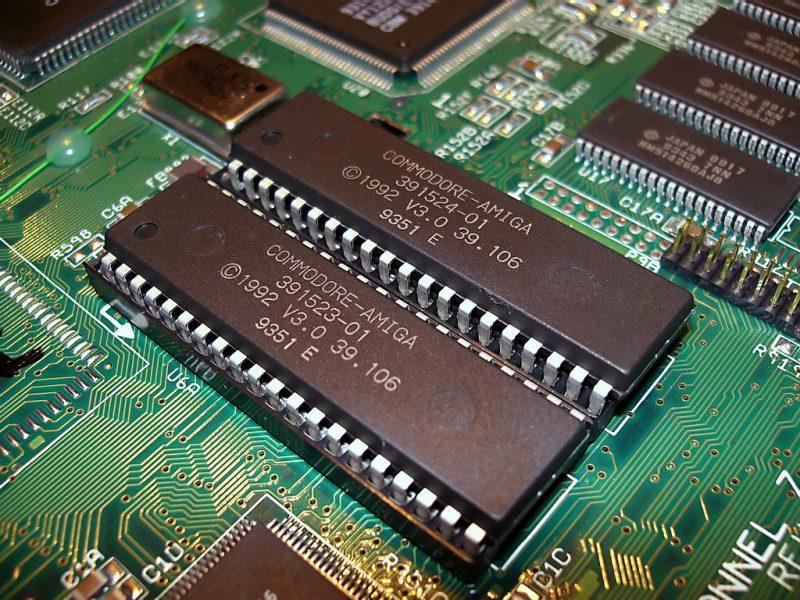

L’impact de l’utilisation du PAL et du PLA? C’était assez important, car il permettait la mise en œuvre de circuits combinatoires et séquentiels sur une seule puce. Par exemple, les systèmes vidéo basés sur une multitude de puces TTL ont été intégrés dans un seul processeur. Deux exemples clairs de l’utilisation des puces PAL et PLA se trouvent d’une part dans le Sinclair ZX81 par rapport au ZX80 et dans le système vidéo de l’Apple Macintosh, où ils ont réussi à intégrer tous les circuits vidéo sur une seule puce, réduction des coûts par rapport à l’Apple Lisa créée par Apple lui-même.

Mais les PAL et les PLA sont rapidement devenus obsolètes et de nouveaux types de logique programmable sont apparus au fil du temps. Aujourd’hui, ceux qui se démarquent le plus sont les FPGA, mais ce ne sont pas les plus utilisés, mais les CPLD.

Qu’est-ce qu’un CPLD et comment se compare-t-il à un FPGA?

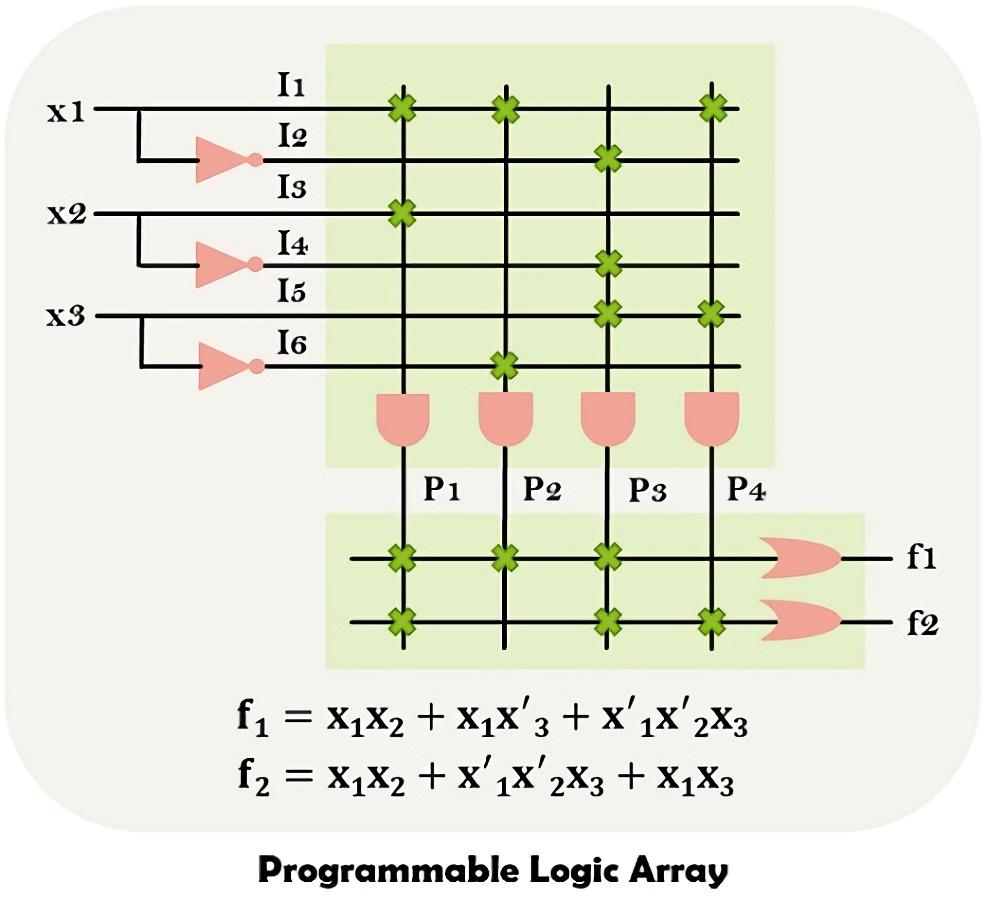

Un CPLD, dont l’acronyme signifie Complex Programmable Logic Device, comme un FPGA est un type de logique programmable, mais dont le fonctionnement dérive de ROM, PLA et PAL. Son architecture et son fonctionnement sont donc totalement différents de ceux des FPGA.

Grâce aux différences avec un FPGA, vous comprendrez ce que sont les CPLD et où et comment ils sont utilisés.

- Les FPGA sont mieux préparés pour simuler du matériel qui dépend du temps, des cycles d’horloge, tandis qu’un CPLD est plus conçu pour quoi avec des circuits combinatoires et ne dépend donc pas d’une séquence d’étapes par cycle.

- Dans un CPLD, le temps nécessaire à une fonction synthétisée dans celui-ci sera toujours le même, dans un FPGA, ce ne sera pas le cas. Par conséquent, les CPLD sont utilisés pour concevoir des circuits combinatoires.

- Les FPGA sont considérés comme des produits très haut de gamme et donc avec un coût élevé. Le CPLD au contraire.

- Les FPGA peuvent fonctionner à des vitesses d’horloge beaucoup plus élevées qu’un CPLD.

- Un FPGA doit être reprogrammé à chaque fois qu’il est allumé, car il est déprogrammé lorsqu’il est éteint, un CPLD fonctionne comme une ROM et il ne perdra pas sa configuration lorsque l’appareil est éteint. Cela signifie que les FPGA sont basés sur la RAM dans leur architecture et les CPLD sur la ROM.

Nous ne verrons donc jamais quelque chose de complexe comme un CPU implémenté dans un CPLD, car ils ne sont pas conçus pour cela. Aujourd’hui, les CPLD sont souvent intégrés dans les cartes de développement FPGA, il est donc courant de combiner les deux types de circuits programmables.

Comment fonctionne un CPLD?

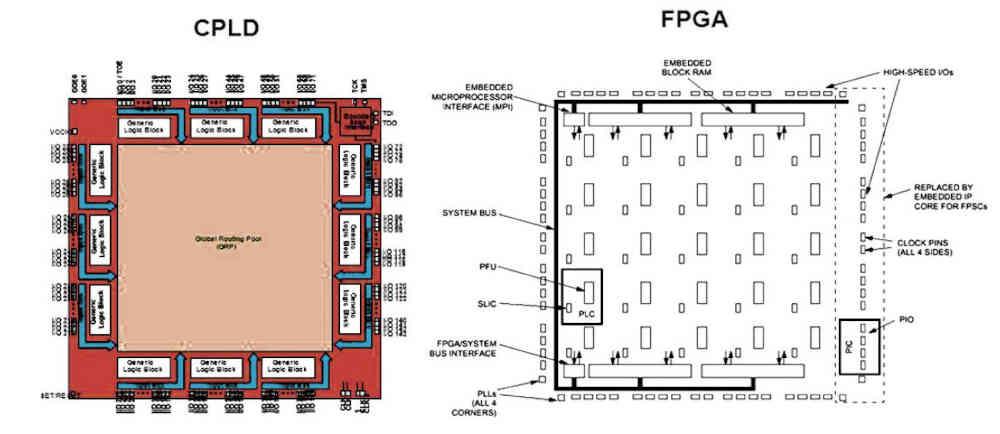

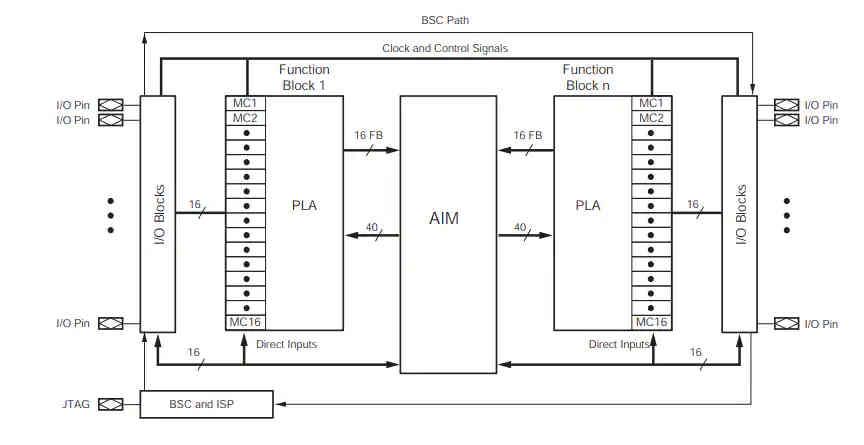

Un CPLD n’est fondamentalement rien de plus qu’une version améliorée et donc plus complexe d’un dispositif PLD. Que sont les appareils PLD? Nous les avons déjà dit et ils sont ce qu’on appelait PLA à leur époque.

Un CPLD n’est rien de plus qu’une série de PLA en tant que fonction d’entrée, mais ses portes OU ne génèrent pas de sortie, mais sa sortie est distribuée via une matrice qui se connecte à une autre série de fonctions PLA, ce qui peut donner une sortie ou une alimentation de résultat. retour dans la direction opposée.

Dans un CPLD, par conséquent, toutes les fonctions logiques possibles sont codées dans les différents PLA qui sont combinés pour réaliser la fonction finale à obtenir. En général, dans la conception de nouveaux processeurs, les CPLD sont utilisés à la fois pour simuler la logique combinatoire et la fonction fixe, tandis que les FPGA sont utilisés pour la logique séquentielle et des éléments plus complexes tels que les ALU. Par curiosité, les instructions des unités de décodage des CPU et GPU sont généralement implémentées en premier dans CPLD, car au fond elles ne sont rien de plus que des circuits combinatoires.