Ce que font AMD et TSMC est très impressionnant, peut-être pas au niveau d’Intel avec Foveros (pour l’instant) mais ce qui est sûr c’est que même si technologiquement ils ne sont pas à la hauteur pour l’instant, en performances ils vont se positionner comme leaders (sauf surprise avec Alder Lake-S).

AMD Zen 3 3D Cache, un bond de performance de 15% dans le gaming

Les chiffres glissés par Lisa Su donnent ce chiffre comme un résultat moyen, mais maintenant nous connaissons les curiosités des pourquoi. Et c’est que l’ajout d’une puce verticale supplémentaire en tant que cache accru ne sera pas, comme on le supposait, un cache de niveau 4, ou en d’autres termes, ce ne sera pas techniquement le Victim Caché typique.

Tout est beaucoup plus simple de la théorie, mais de la pratique les chiffres sont accablants et nous nous expliquons.

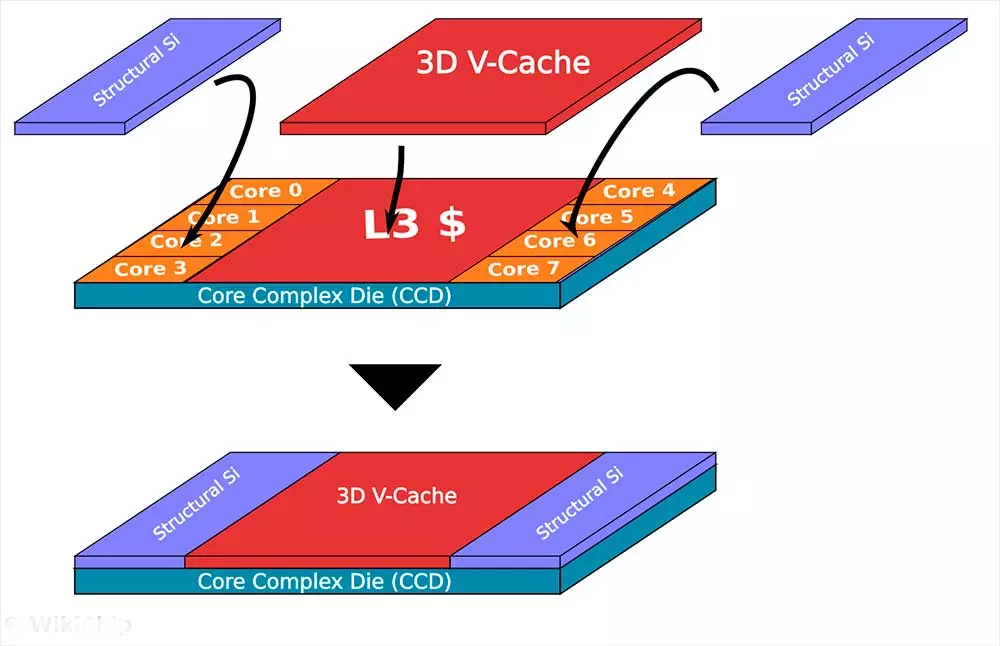

Ce qu’AMD réalise avec ce cache vertical, c’est que Windows et les CCD voient la puce ajoutée comme « transparente », c’est-à-dire qu’il n’y a aucun changement physique pour le logiciel ou pour le matériel dans leur mode de fonctionnement entre les cœurs et l’IOD.

Ce que vous verrez est un bloc de cache L3 de plus, qui sera fabriqué à 7 nm par TSMC et mesurera 6 x 6 mm (36 mm2) connecté directement aux caches CCD via TSV. Et voici la magie, car dans le cas du 5950X qui était montré à l’époque avec cette technologie, on parle de pas moins de 192 Mo de L3 au total pour les 64 existants du modèle d’origine que l’on peut actuellement acheter.

TSV chiffres vertigineux, à la hauteur d’Intel

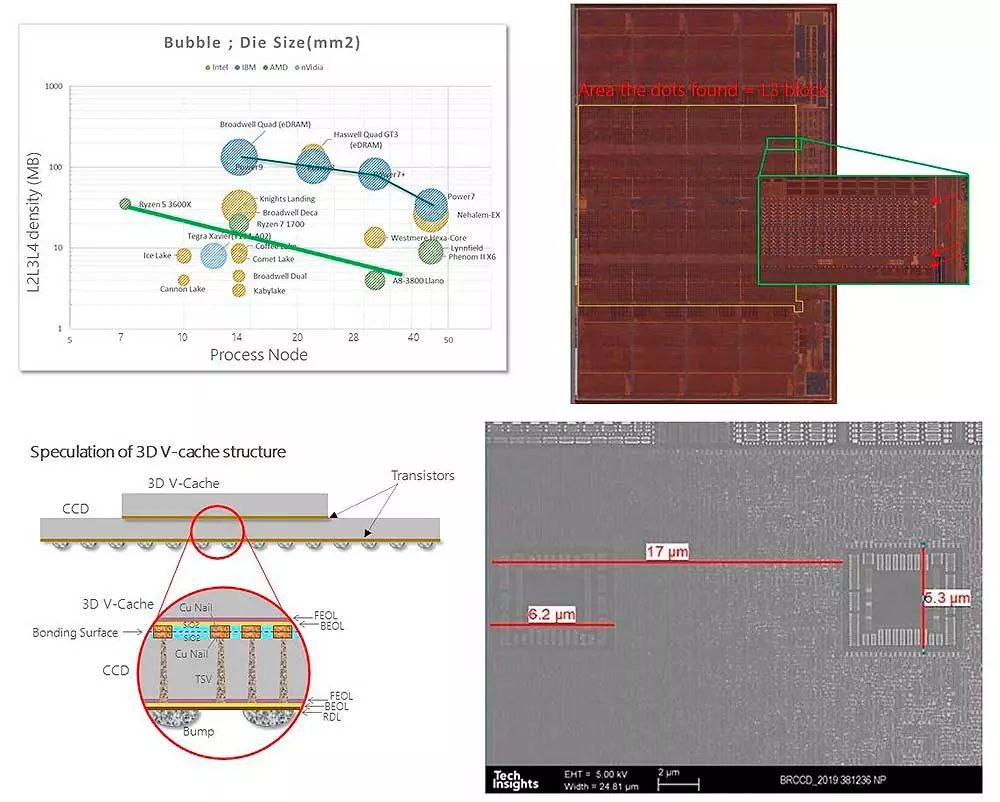

Chaque CPU disposera de plus de 2 To/s de bande passante grâce à ce nouveau cache et ses connexions TSV, dont on sait désormais qu’elles sont faites par bosses dans ce qu’on appelle « Face cachée », Chaque TSV est connecté du FEOL de chaque CCD au Surface de liaison par Clous en cuivre. Ils sont en contact direct avec le BEOL de ce nouveau cache, qui permet l’échange d’informations à partir des substrats et des caches.

Pour nous donner une idée de la complexité de tout cet empilement vertical, on calcule que pour chaque partition L3 de 4 Mo qui possède un CCD il y a 3000 TSV avec une taille qui les inclut entre 6,1 µm et 17,3 µm d’épaisseur.

Pour la quadrature du cercle, des données plus stratosphériques sont fournies, car dans la SMU, elles sont calculées 56 TSV et 14 plus dans la zone dite de test.

Qu’avons-nous au total dans le nouveau 5950X ? Eh bien, un énorme 24070 TSV pour connecter les deux substrats, là où, comme nous l’avons dit précédemment, la surface du nouveau cache AMD 3D n’est que de 36 mm2. Des chiffres sans aucun doute stupéfiants et qui permettront à AMD de battre Intel, au moins momentanément.