Les modules de mémoire NV-DIMM ont la particularité d’avoir à l’intérieur de la RAM non volatile ou du Flash NAND, parmi lesquels se distingue le NVDIMM-P, qui est basé sur le placement de la RAM et de la mémoire Flash NAND dans un seul module DIMM, partageant avec lui la mémoire autobus. Eh bien, AMD adoptera la mémoire NVDIMM-P dans les futurs processeurs et APU. Nous expliquons comment ils vont l’implémenter sur leur matériel.

L’une des futures améliorations que nous allons voir à la fois dans le CPU, le GPU et l’APU est la Intégration du contrôleur flash dans le processeur comme cela s’est produit en son temps avec le contrôleur de mémoire RAM. Ceci, en combinaison avec l’interface Compute Express Link ou CXL, une variante de PCI Express 5.0 et versions ultérieures, permettra une communication conjointe avec la mémoire Flash NAND et la RAM système. Ainsi, à l’avenir, nous aurons des modules de mémoire qui intégreront la mémoire et le stockage dans un seul module.

On sait que nous aurons Modules NVDIMM qui combinent les Mémoire DDR5 avec mémoire NAND FLASH dans un seul DIMM. La communication avec le processeur peut se faire via une interface PCIe 5.0. N’oublions pas que Samsung a récemment introduit une extension de mémoire DDR5 pour un port PCIe avec interface CXL. Les modules DDR pourraient-ils disparaître au profit des interfaces PCIe ? Eh bien, AMD a pensé à cette possibilité pour l’avenir.

AMD implémentera des interfaces NVDIMM-P dans ses futurs processeurs

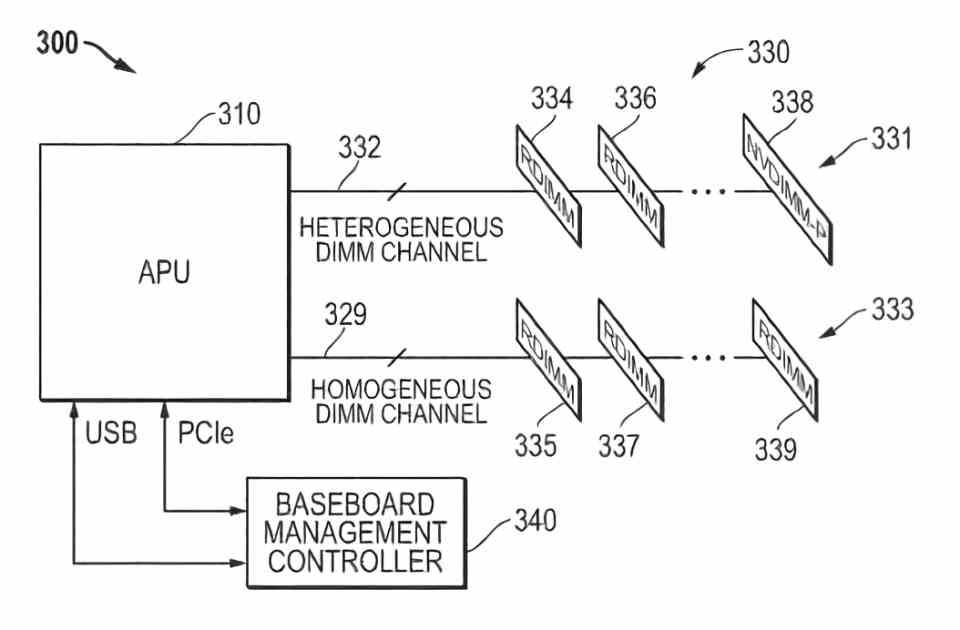

La source de cette nouvelle n’est rien de plus qu’AMD lui-même, en particulier un brevet intitulé RAPPORT D’ERREUR POUR LES MODULES DE MÉMOIRE NON VOLATILES où il parle de la mise en œuvre d’une interface mémoire NVDIMM-P pour le processeur et de toutes les modifications qui doivent être apportées pour le faire.

Dans la description dudit brevet on peut lire ce qui suit :

Les systèmes informatiques utilisent couramment des puces de mémoire vive à haute densité (DRAM) comme mémoire principale. La plupart des puces DRAM vendues aujourd’hui sont compatibles avec diverses normes DDR promulguées par le Joint Electron Devices Engineering Council (JEDEC). Les contrôleurs de mémoire DDR sont utilisés pour gérer l’interface entre les différents agents (accédant à ces mémoires) et les DRAM DDR conformément aux normes DDR publiées.

Un module de mémoire double en ligne non volatile avec stockage persistant (« NVDIMM-P ») est un type de mémoire de stockage qui est utilisé à la place des DIMM DDR standard, mais inclut une mémoire persistante. Cependant, ces mémoires contiennent différents types de conditions d’erreur qui diffèrent des conditions d’erreur DDR. De plus, les conditions d’erreur associées au NVDIMM-P ont des effets d’erreur différents sur le système d’exploitation exécutant des processus utilisant la mémoire que les conditions d’erreur associées aux DIMM DDR.

Le brevet confirme donc qu’AMD a développé un moyen d’utiliser ce type de modules de mémoire dans vos futurs processeurs. Pour le moment, on ne sait pas dans quelle génération il sortira. Mais si l’on fait preuve de logique il est clair qu’un futur AMD EPYC 7004 basé sur l’architecture Zen 4 pourrait être un bon candidat pour l’utilisation de ce type de mémoire.