Sur le PC, diverses interfaces communiquent entre elles avec le CPU, l’APU ou le GPU. Mais quelle est la pièce qui unifie les différents signaux qui entrent et sortent d’un processeur ? Nous expliquons ce que cette pièce commune se trouve dans tout le matériel et comment cela fonctionne. Ce qui est communément appelé SerDes.

Qu’est-ce qu’un SerDes ?

Les SerDes ont leur origine dans le monde des télécommunications. La raison de son existence est assez simple, envoyer des données via un seul câble au lieu de plusieurs en même temps réduit la complexité de l’interphone interne d’un réseau de télécommunications. Maintenant, si nous y réfléchissons, la manière dont les différentes parties logiques et mémoire d’un processeur et d’un système sont communiquées se fait par une série de câbles.

À première vue, en termes de performances, il peut sembler que l’utilisation d’une interface parallèle est toujours bien meilleure, mais il existe un certain nombre de facteurs qui améliorent les interfaces série. Quels sont? Tout d’abord, les interfaces parallèles prennent beaucoup plus de place et sont plus sensibles aux ondes électromagnétiques, en plus de consommer plus à la même vitesse d’horloge. L’inconvénient des interfaces série est qu’elles ont une latence plus élevée dans l’envoi de données.

Cependant, dans une conception matérielle, il existe des pièces avec une interface série et d’autres avec une interface parallèle. Comment les connecter entre eux leurs interfaces de communication sont différentes ? Eh bien, avec un SerDes, dont le travail principal est de communiquer divers éléments, notamment des périphériques avec le CPU.

Tous les chemins mènent à Rome

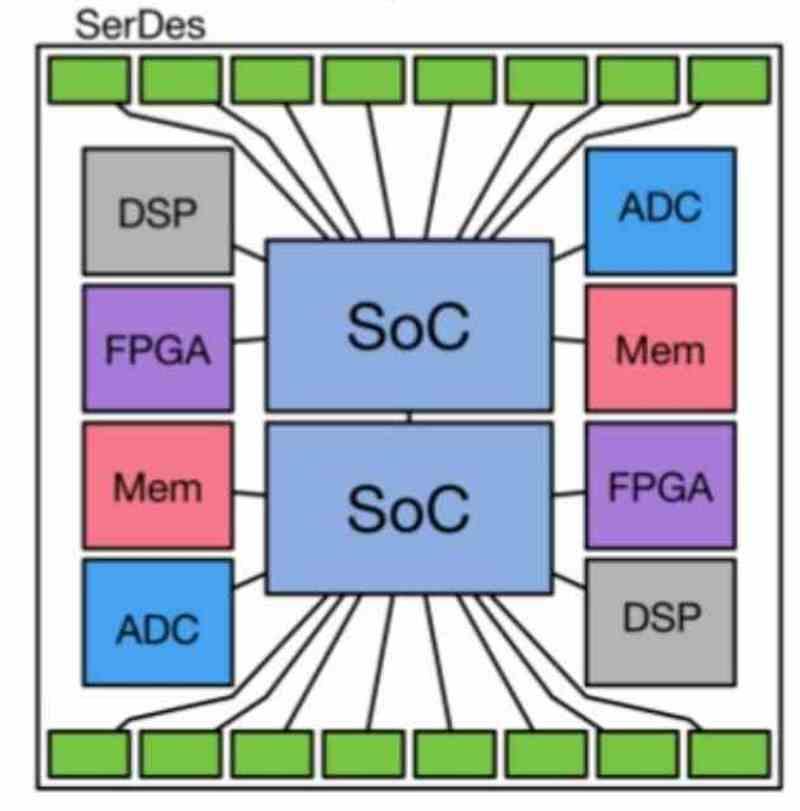

Jetez un œil à votre PC et aux différentes interfaces pour les composants internes et les périphériques externes. Nous avons des interfaces comme SATA, PCI Express, USB et bien d’autres. Chacun d’eux dispose d’interfaces pour différents types de périphériques. Eh bien, en interne, chacune de ces interfaces ne se connecte pas directement au concentrateur du processeur central, mais plutôt à une série de SerDES.

Sans surprise, il existe différentes interfaces d’entrée et de sortie pour les périphériques de toutes sortes qui sont conçues pour interagir avec les spécifications standard des différents SerDes. Quelles sont ces interfaces ? Eh bien, nous avons le cas des interfaces PCI Express dans leurs différentes technologies, pour le stockage comme le SATA et le SAS, pour la transmission vidéo comme le DisplayPort et le HDMI, pour les réseaux comme les différentes interfaces ethernet gigabit, etc. Mais, la chose ne se limite pas seulement aux interfaces d’E/S pour les périphériques et les composants, mais la chose va plus loin et la mémoire RAM communique également via un SERDES avec le hub central que possède chaque processeur, appelé Northbridge et qui est en charge de communiquer les différents éléments entre eux et chacun d’eux avec la mémoire RAM.

Par conséquent, les différentes interfaces non seulement lors de la conception, mais également dans l’évolution, doivent tenir compte de l’évolution de SerDes à ce moment précis, puisque ces interfaces seront connectées à celles-ci dans la logique interne de chaque circuit intégré. Il faut prendre en compte qu’en interne dans un processeur s’il y a trop d’interconnexions alors la complexité de l’intercommunication sera trop grande. Il est donc préférable de réduire le nombre d’interconnexions en sérialisant les données entrantes en échange d’une augmentation de la vitesse d’horloge.

Comment fonctionne un SerDes ?

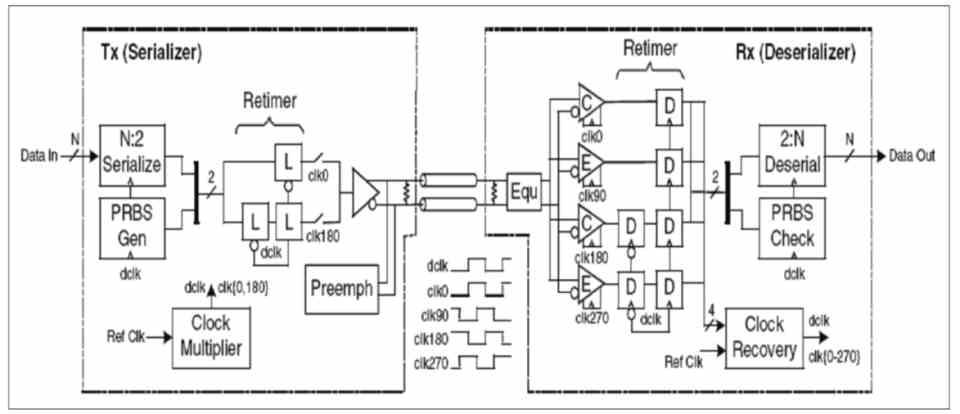

Si l’on prend en compte cette définition pure et simple, alors un SerDes est toujours un élément matériel composé d’un multiplexeur et d’un démultiplexeur, qui sont deux types de systèmes combinatoires de base. Ce qu’un multiplexeur ou MUX fait, c’est convertir un seul signal en plusieurs signaux différents et un démultiplexeur ou DEMUX fait la tâche opposée.

La différence est que le SerDES prend en compte la vitesse d’horloge, car selon le moment où les données sont transmises, l’interprétation par le processeur est l’une ou l’autre. En d’autres termes, lorsqu’une demande de données est faite à partir de n’importe quel composant d’un système matériel, il y a des moments et donc une fenêtre d’opportunité pour transmettre les données. En quoi cela se traduit-il ? Eh bien, les données sont transmises suivant un temps et cela implique donc un signal d’horloge.

Supposons que nous voulions sérialiser un signal parallèle qui est transmis via une série de lignes Full Duplex, qui transmettent 1 bit d’information dans chaque direction. La bande passante est de 1,25 Gbps, cela signifie donc que chacune des lignes fonctionne à 625 MHz. Nous avons quatre lignes au total, donc si nous sérialisons le signal, nous parlerons d’un signal à 5 Gbps, ce qui dans le cas de une ligne Full Duplex nécessitait que l’interface série fonctionne à 2,5 GHz. Le chemin inverse est donc facile à comprendre, on peut transmettre le signal de 5 Gbps à travers deux lignes en utilisant une vitesse de 1,25 GHz pour chaque ligne, à travers quatre lignes en utilisant une vitesse d’horloge de 625 MHz chacune, et ainsi de suite.

L’évolution du SerDes

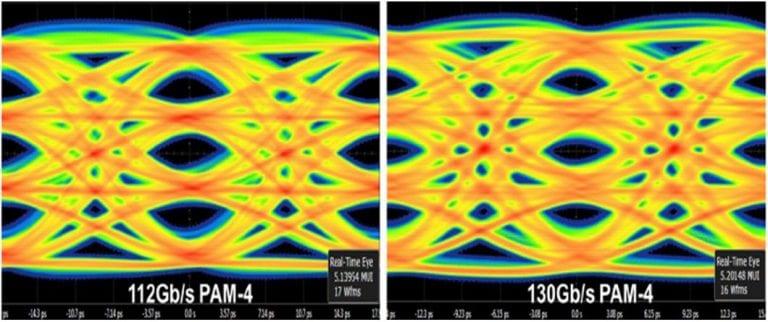

Avant d’avoir commenté comment SerDES influence complètement la conception des futures interfaces d’entrée et de sortie, ce qui implique que le développement des futures interfaces ou des évolutions des interfaces existantes dépend entièrement des SerDes auxquels elles sont connectées, puisqu’elles doivent pouvoir communiquer avec eux. Par exemple, SerDES à 112 Gbps, le plus rapide à ce jour du marché, utilise la signalisation PAM4, donc ce type de signalisation sonne pour des interfaces comme le futur PCI Express 6.0.

Cependant, faire progresser la vitesse de communication de SerDes n’est pas une tâche facile, à chaque nouvelle génération dans laquelle la bande passante de communication est augmentée, de nouveaux défis apparaissent, notamment avec les éléments qui dégradent la qualité du signal utilisé. Nous ne pouvons pas non plus oublier que la tension n’évolue pas de la même manière que la vitesse d’horloge, ce qui fait monter en flèche la consommation électrique des interfaces. D’où l’adoption d’interfaces PAM4 pour éviter d’augmenter la vitesse d’horloge à des limites qui ne seraient pas acceptables.

Pour le moment, seule la mémoire GDDR6X de NVIDIA RTX 30 utilise l’interface PAM4, ce qui signifie que les SerDes internes de ces GPU utilisent ce type d’interface pour communiquer avec le GPU. Ce qui influence le reste des interfaces I/O de ces GPUs. En même temps, cela complique l’adoption d’un système PAM4 dans d’autres systèmes, car cela signifie que les interfaces doivent s’adapter aux règles temporelles des SerDes inclus dans le processeur.