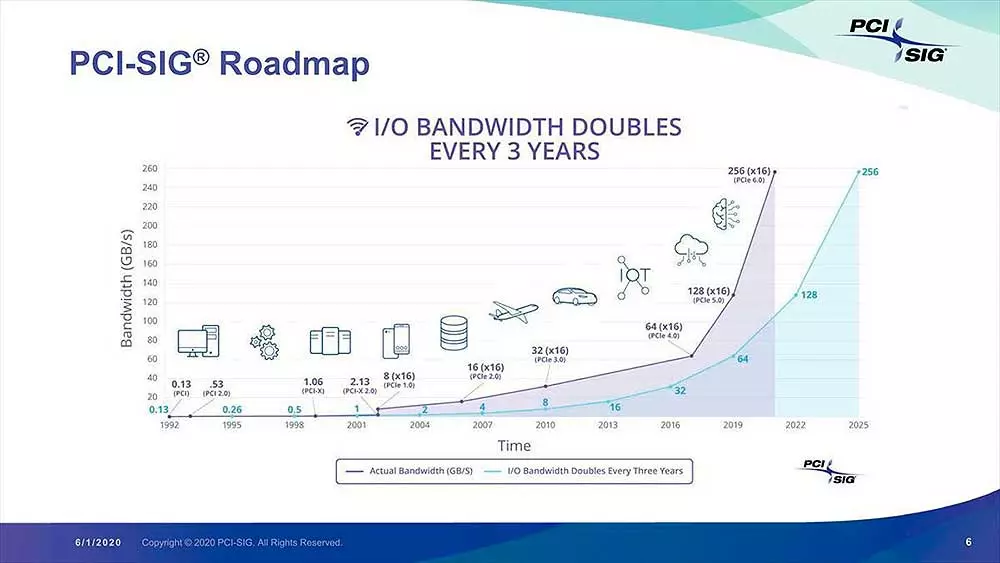

Le PCI Express 6.0 suit d’emblée les mêmes améliorations que les générations précédentes de cette interface, c’est-à-dire qu’il est basé sur le doublement de la bande passante par rapport à la génération précédente. Cependant, dans le cas du PCI Express 6.0, de profonds changements ont été nécessaires dans le développement de la sixième génération de cette interface.

La bande passante du PCI Express 6.0 est de 128 Go/s pour une interface 16 lignes, une bande passante exagérément élevée pour une interface I/O et c’est un saut de quatre fois par rapport au PCI Express 4.0 actuel que nous utilisons pour les cartes graphiques actuelles . Le saut signifie également un saut des contrôleurs flash NVMe SSD de 7-8 Go/s à 28-32 Go/s avec PCI Express 6.0.

Rétrocompatibilité et problème d’instabilité du signal

L’interface PCI Express a toujours été rétrocompatible avec les versions précédentes du protocole, cela signifie que nous pouvons brancher une carte PCI Express 1.0 dans un slot PCI Express 6.0 et cela fonctionnera car le pinage sera exactement le même. Il n’est donc pas possible d’augmenter le nombre de broches pour augmenter la bande passante sans augmenter la vitesse. La solution? Augmentez la vitesse d’horloge à laquelle l’interface fonctionne.

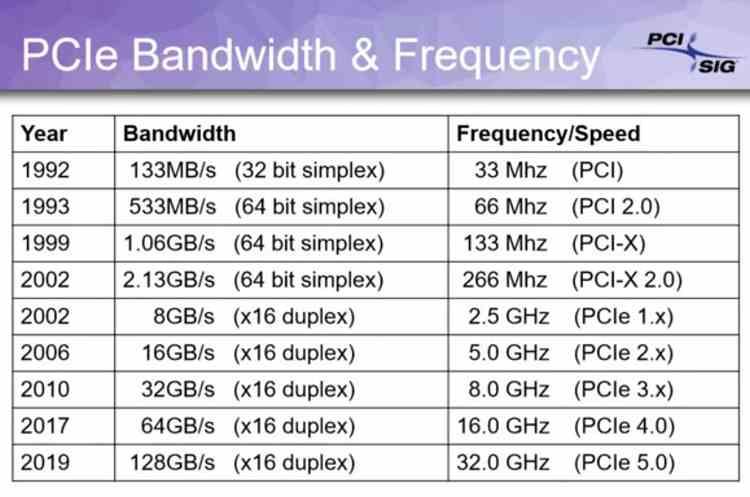

Le problème avec PCI Express 6.0 ? Au fur et à mesure que nous augmentons la vitesse d’horloge d’une interface, celle-ci devient plus instable avec la distance et après six générations, ils ont dû apporter des modifications à l’interface en raison de la vitesse élevée à laquelle l’interface fonctionne de manière traditionnelle. Et est-ce que si vous regardez le tableau qui accompagne ces lignes, nous parlons d’une vitesse théorique de 64 GHz, ce qui déforme suffisamment le signal, même à courte distance, les deux extrémités sont dans une interface PCI Express.

Cela a rendu nécessaire l’adoption d’une série de mesures pour rendre possible le saut vers le PCI Express 6.0.

Première des améliorations de PCI Express 6.0, l’utilisation de PAM4

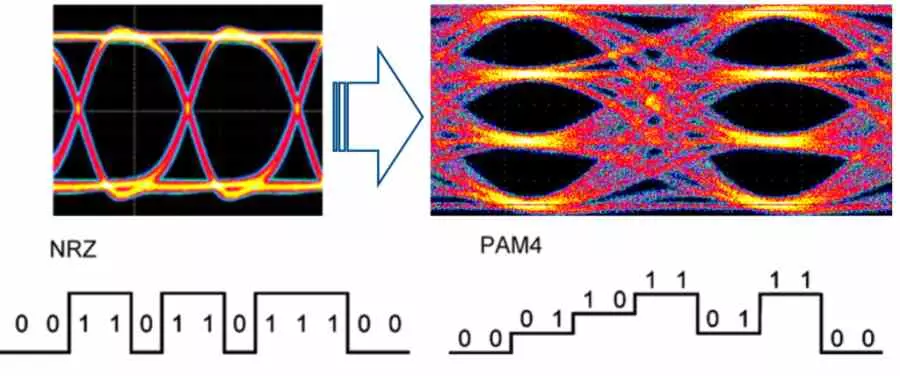

Comment une interface externe ou interne d’une puce sait-elle si la valeur est un 1 ou un 0 ? Eh bien, simple, en fonction de la tension dans laquelle l’information est transmise. Les systèmes binaires sont basés sur l’utilisation de deux tensions avec suffisamment de distance entre elles pour que la chute ou l’augmentation de la tension rende le signal non confus. Dans les systèmes analogiques une simple variation de la tension suppose un changement de l’information. Pour cette raison, les ordinateurs parlent en binaire.

Qu’est-ce que cela a à voir avec PCI Express 6.0 ? Puisqu’on ne peut pas augmenter la bande passante car le signal est déformé et ni le nombre de broches pour la rétrocompatibilité, une solution doit être trouvée et cela passe par l’utilisation de l’encodage PAM4 ou Pulse Amplitude Modulation, que nous avons déjà vu dans la GDDR6X et n’est pas basé sur l’utilisation de deux valeurs de tension mais de 4 valeurs de tension pour chaque broche. De cette façon, nous pouvons encoder les valeurs 00, 01, 10 et 11 sur chaque broche. Quatre valeurs au total, au lieu des deux valeurs classiques qui seraient 0 ou 1.

La solution évite d’augmenter la bande passante et les broches, mais elle anticipe que dans PCI Express 7.0, cela ne sera plus possible à partir des méthodes conventionnelles. Nous verrons peut-être l’utilisation de la photonique et des interfaces optiques, mais avec les améliorations apportées au PCI Express 6.0 tout juste sorti du four, mieux vaut être patient avec son successeur.

Changements dans le système de paquets

Le passage à PAM-4 a changé la façon dont l’interface PCI Express 6.0 envoie ses paquets, malgré le fait qu’elle soit compatible avec les générations précédentes en communiquant en mode traditionnel PAM-2 ou NRZ. La réalité est que le format PAM-4 ne prend pas en charge le système de paquets précédent et que le protocole de communication a donc changé à cause de cela.

Le premier changement a été ce que l’on appelle la correction d’erreur directe ou FEC, qui est le nouveau protocole pour corriger les erreurs dans l’envoi de données. Le problème est que la bande passante à traiter est si élevée que le FEC ajoute une latence énorme lors de l’envoi des données. Pour pallier cela, la norme PCI Express 6.0 utilise un type de package appelé FLIT. Un paquet n’est rien de plus qu’un ensemble de bits avec une destination spécifique. La latence d’envoi de chaque FLIT ? Cela dépend du nombre de lignes sur l’interface, mais chaque paquet a une latence de seulement 2 ns sur un PCI Express 6.0 à 16 lignes, mais va jusqu’à 32 ns sur une interface à une seule ligne.

Le FEC ne fonctionne qu’avec des tailles fixes, c’est pourquoi le FLIT a une taille de 256 octets par envoi. Chaque paquet ou TLP peut avoir une taille allant de 0 octet à 4096 octets et donc chaque paquet peut être composé de plusieurs FLITS.

Troisième mise à niveau vers PCI Express 6.0, consommation variable

PCI Express 6.0 ajoute un nouvel état de faible consommation appelé L0P. Ce mode permet à l’interface de réduire sa consommation électrique lorsque le flux de données envoyé est inférieur à celui que l’interface peut transmettre. Pour ce faire, la vitesse d’horloge à laquelle l’interface fonctionne à des moments précis de la transmission des données varie, le tout sans provoquer d’arrêt qui ajoute de la latence à la transmission des données.

Le problème est que ce mécanisme est associé à FLITS et FEC et donc à PAM4, ce qui signifie qu’il n’est possible de l’utiliser qu’en mode PCI Express 6.0 et pas dans les autres modes.