Ce qui est présenté par Intel est centralisé en deux parties très bien différenciées : les cœurs dits efficaces ou E-Cores et les cœurs de performance, maintenant appelés P-Cores. L’objectif de l’entreprise est de créer une série de silicones capables de faire évoluer les charges de travail multicœurs et horizontalement sur l’ensemble d’entre elles. En outre, la société a fourni un certain nombre de nouvelles et de données très intéressantes qui méritent d’être mentionnées.

Intel Alder Lake, une architecture pour tous les segments de bureau

Le dilemme d’Intel était clair : il devait affronter AMD et Apple dans deux secteurs totalement différents, le premier en hautes performances et le second en rapport efficacité/performance par watt. Logiquement, ils n’ont rien à voir là-dedans, mais l’entreprise avait vraiment la possibilité de se diversifier ou d’opter pour ce que nous allons voir ensuite.

Cœurs efficaces ou E-Cores

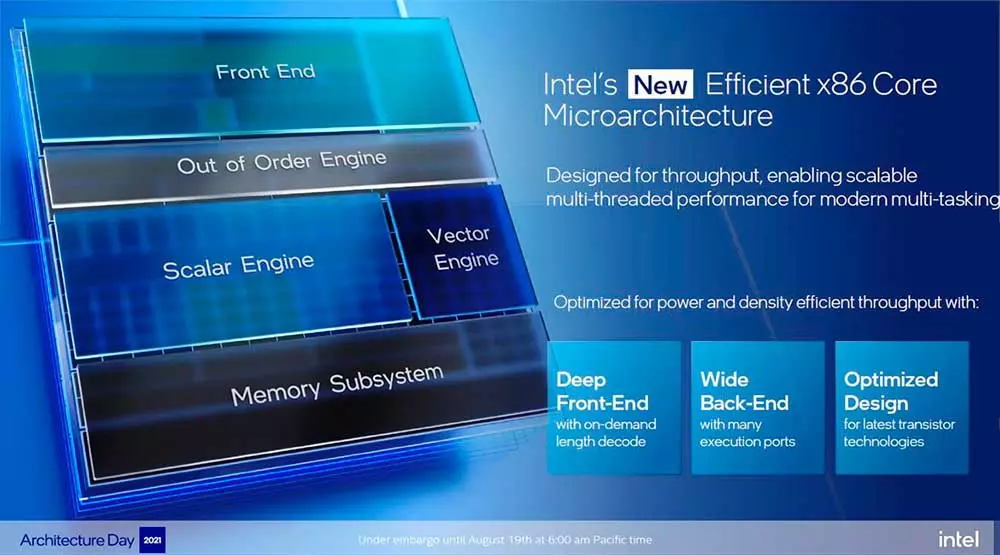

La microarchitecture des cœurs efficaces ou E-Cores est Gracemont, pensés et conçus pour une efficacité où la chose la plus frappante sera la quantité de gammes de fréquences qu’ils supporteront, ainsi que les basses tensions qui réduiront la consommation totale d’énergie.

Les cœurs efficaces utilisent une variété d’avancées techniques pour hiérarchiser les charges de travail sans gaspiller la puissance de traitement et pour améliorer directement les performances avec des fonctionnalités qui améliorent l’instruction par cycle (IPC) :

- Le cache cible a 5 000 branches d’entrée, ce qui se traduit par une prédiction de branche plus précise.

- Cache d’instructions de 64 kilo-octets pour garder les instructions utiles à portée de main sans gaspiller de la mémoire ou de la puissance du sous-système.

- Alder Lake possède le premier décodeur de longueur d’instruction à la demande d’Intel qui génère des informations de pré-décodage.

- Décodeur en cluster Intel qui permet de décoder jusqu’à six instructions par cycle tout en maintenant l’efficacité énergétique.

- Un back-end complet avec un mappage sur cinq et huit larges, 256 entrées dans le désordre pour Windows et 17 ports d’exécution.

- Technologie d’application Intel Control-flow Enforcement Technology et Intel Virtualization Technology Redirection Protection.

- La mise en œuvre d’AVX ISA, ainsi que de nouvelles extensions pour prendre en charge des opérations complètes d’intelligence artificielle.

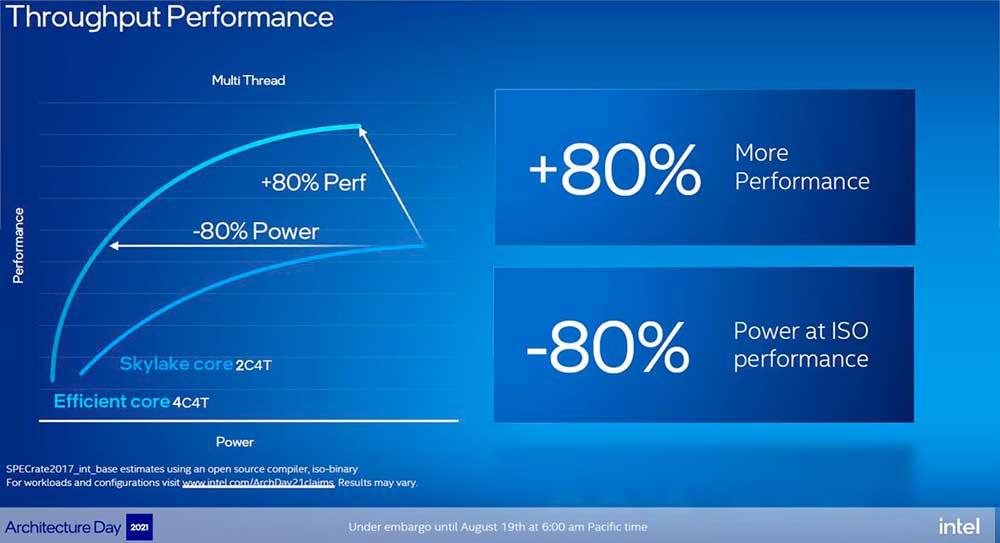

Intel fait une curieuse comparaison, puisque le plus logique était de mesurer les données de performances d’Alder Lake avec Rocket Lake, qui est l’architecture qu’il remplace, mais ils se sont concentrés sur Skylake en tant que tel pour affirmer que leur nouvelle architecture atteint des performances Single Core A 40% plus de performances avec la même puissance ou les mêmes performances tout en consommant moins de 40% d’énergie.

Dans le même temps, ils affirment que les noyaux efficaces offrent une 80% plus de performances tout en consommant moins d’énergie que deux cœurs Skylake avec leurs quatre threads ou les mêmes performances que ceux-ci tout en consommant un 80% moins d’énergie.

Cœurs de performance ou P-Cores

Quant aux cœurs P-Core ou Performance Core d’Intel, ils arrivent avec la microarchitecture Crique d’or Et logiquement, ils sont conçus pour atteindre des performances maximales, réduire les latences et améliorer en un seul thread ce que Rocket Lake a déjà fait. Par conséquent, les changements qu’Intel cite sont les suivants :

- Plus étendu : six décodeurs (au lieu de quatre) ; huit cache µop larges (au lieu de six) ; six devoirs (sur cinq); 12 ports d’exécution (au lieu de 10).

- Plus profond – Fichiers journaux physiques plus volumineux ; Tampon de réorganisation plus profond avec 512 entrées.

- Plus intelligent : amélioration de la précision de la prédiction des branches ; latence L1 effective réduite ; optimisations de bande passante en écriture prédictive sur L2.

Les P-Cores sont les cœurs de processeur les plus performants qu’Intel ait jamais construits et repoussent les limites de la faible latence et des performances des applications à thread unique avec :

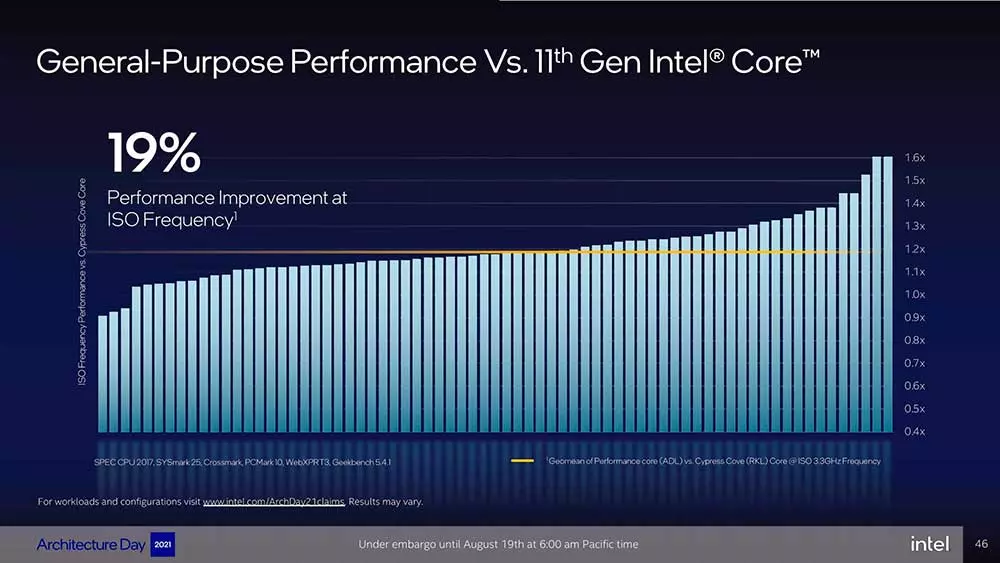

- ~ 19 % d’amélioration de la moyenne géographique sur un large éventail de charges de travail par rapport à la 11e génération actuelle (Crique de cyprès) à la fréquence ISO pour les performances à usage général.

- Exposition à plus de parallélisme et augmentation du parallélisme d’exécution.

- Intelligence Extensions matricielles avancées, une percée pour l’accélération de l’IA de nouvelle génération, ainsi que l’inférence d’apprentissage en profondeur et les performances d’entraînement. Il comprend du matériel dédié et une nouvelle architecture de jeu d’instructions pour effectuer des opérations de multiplication matricielle beaucoup plus rapidement.

- Latence réduite et meilleure compatibilité avec les applications de données et de code volumineuses.

Directeur de thread Intel

C’est probablement la plus remarquable en termes d’innovations technologiques dans son ensemble. Intel garantit que pour que les cœurs de performance et les cœurs efficaces fonctionnent correctement avec le système d’exploitation, Intel a développé une technologie de programmation améliorée appelée Intel Thread Director.

Construido directamente en el hardware (evidentemente no es software), Thread Director proporciona telemetría de bajo nivel sobre el estado del núcleo y la combinación de instrucciones del hilo, ayudando y dirigiendo al sistema operativo para colocar el hilo correcto en el núcleo correcto en el momento C’est Correct.

Par conséquent, Intel Thread Director est dynamique et adaptable, adaptant les décisions de planification aux besoins informatiques en temps réel. C’est important, car jusqu’à présent, l’OS était celui qui prenait les décisions en fonction des statistiques et des temps d’utilisation, tandis qu’Intel Thread Director change la donne :

- Utilisation de la télémétrie matérielle pour diriger les threads qui nécessitent des performances plus élevées vers le P-Core approprié à ce moment-là.

- Surveille le mélange d’instructions, la santé du noyau et d’autres télémétries microarchitecturales pertinentes, aidant le système d’exploitation à prendre des décisions de programmation plus intelligentes.

- Optimisation de Thread Director pour de meilleures performances sur Windows 11 en collaborant avec Microsoft.

- L’agrandissement de la API PowerThrottling, qui permet aux développeurs de spécifier explicitement des attributs de qualité de service pour leurs threads.

- Appliquer une nouvelle classification EcoQoS qui informe le planificateur si le thread préfère un E-Core (de tels threads sont planifiés sur des cœurs efficaces).

Intel Alder Lake : Process Intel 7 et autres actualités générales

Comme nous le savions déjà, Intel va introduire son processus Intel 7 comme architecture générale et en tant que tel, l’efficacité a changé. Maintenant, avec Alder Lake, nous pouvons avoir un TDP de 9 à 125 watts, des PC de bureau aux UltraBooks, chacun avec ses processeurs correspondants (pas encore présentés logiquement).

Dans sa configuration maximale on parle d’un processeur (supposé i9-12900K) avec 8 P-Cores et 8 E-Cores, où la curiosité est que seuls les premiers auront HyperThreading. Par conséquent, le nombre de threads s’élève à un maximum de 24 fils.

Quant à son iGPU, on parle du nouveau Xe avec rien de moins que 96 UE, c’est pourquoi il devrait surpasser les APU AMD sur ce point remarquable. Qu’en est-il de l’IPC ? Dans ce cas, Intel a comparé Rocket Lake à Alder Lake et a chiffré l’amélioration d’un thread dans un + 19%, Intel sera donc à nouveau en avance sur AMD, au moins jusqu’à Zen 3+, où ils se reverront.

Une autre nouveauté est son cache LL, techniquement appelé LL Cache, qui obtient 30 Mo et il n’est pas inclusif. Ce cache répond à une nouvelle I/O Fabric pour faire mémoire du sous-système, qui n’atteint rien de moins que 204 Go/s avec bus et fréquences dynamiques pour optimiser l’énergie. Au lieu de cela, le soi-disant Compute Fabric pour les cœurs et l’iGPU atteint jusqu’à 1000 Go/s avec des optimisations en temps réel de la latence du système, qui sera également dynamique pour économiser de l’énergie en cas de besoin.

À propos de ses mémoires, il admet DDR5-4800, LP5-5200, DDR4-3200 et LP4x-4266, ceci comme configuration maximale et sans overclock, c’est-à-dire qu’à partir de ces configurations il est considéré comme overclock pour le BMI. Comme nous le savions déjà et en changeant le registre, Alder Lake sera compatible avec PCIe 5.0, étant la première architecture de bureau à le faire, mais il y a quelque chose que nous devons savoir.

Les voies PCIe 5.0 sont limitées à 16, de sorte que les SSD NVMe M.2 resteront à PCIe 4.0 même si des versions et des modèles sont publiés sous la nouvelle interface. On pourra y remédier à l’avenir avec l’architecture suivante, mais celle-ci aura cette limitation, donc les performances théoriques des SSD continueront à se situer autour de 8000 Mo/s au mieux.