Pour comprendre comment fonctionne le paradigme VISC, nous devons prendre en compte deux concepts différents concernant les performances du processeur. Le premier d’entre eux est le fait que les processeurs PC ont aujourd’hui un ensemble d’instructions internes encore plus petit que RISC, car ce qu’ils font, c’est transférer chacune des instructions dans des micro-instructions plus petites en interne pendant la phase de décodage. Si nous sommes des puristes, la conclusion aujourd’hui tous les processeurs n’est pas qu’ils soient RISC, mais qu’ils ont un jeu d’instructions très réduit qui fonctionne en interne et qui sert à construire le reste des instructions. C’est-à-dire que dès qu’une instruction atteint l’unité de contrôle CPU, elle est décomposée en une liste d’instructions.

La guerre entre RISC et CISC a donc été gagnée par le premier, mais avec le piège que x86, l’architecture CISC la plus utilisée, a fait le piège de se comporter en interne comme un RISC. À ce jour, à l’exception d’ARM, le reste de l’ISA RISC est manquant ou sur le point de disparaître. De plus, même ARM a adopté le concept de division des instructions en instructions plus simples, de sorte que les deux paradigmes en dehors de la définition de l’ISA commun d’une famille sont déjà éteints.

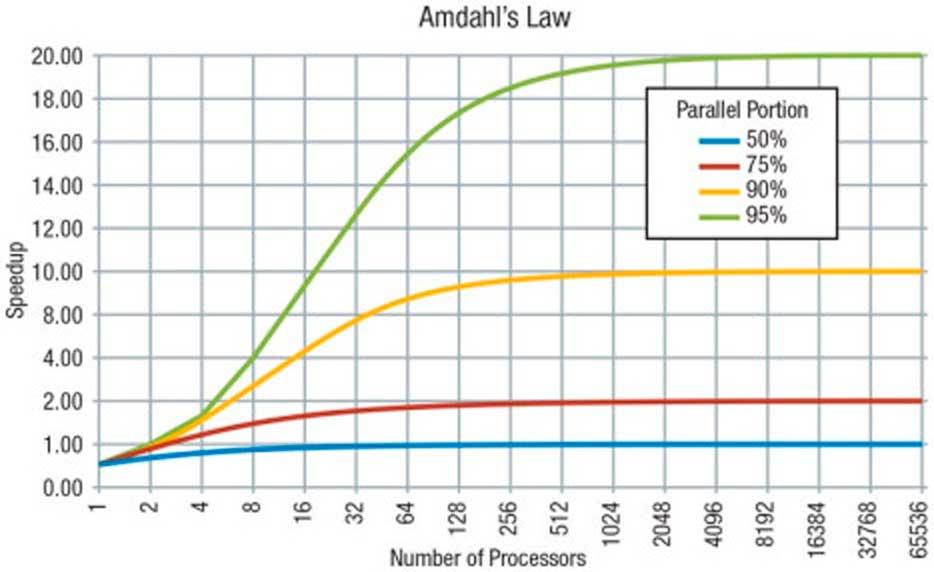

La loi d’Amdahl

Pour comprendre un programme, nous devons comprendre qu’un programme a deux parties différentes :

- Celui qui ne peut être exécuté qu’en série et, par conséquent, ne peut être résolu que par un seul noyau en exécutant un noyau d’exécution solo.

- La partie du code qui peut être exécutée en parallèle, ce qui signifie qu’elle peut être résolue par plusieurs cœurs en même temps et plus il y en a dans le processeur, plus cette partie sera résolue rapidement.

Si nous prenons en compte ce qui a été expliqué dans la section précédente, vous conclurez que certaines des instructions du processeur qui deviennent du microcode deviennent une succession d’instructions qui peuvent fonctionner en série ou en parallèle entre plusieurs cœurs, bien que l’habituel soit que la plupart des instructions sont exécutées dans un seul noyau et que c’est par des éléments partagés que le code est exécuté en parallèle.

Par conséquent, le fait qu’une partie du code soit exécutée par plusieurs cœurs dépend exclusivement du développeur du programme, qui doit explicitement le programmer pour que certaines parties fonctionnent en parallèle.

VISC et cœurs virtuels

Une fois que nous avons déjà expliqué tout ce qui précède, nous pouvons expliquer ce que signifie l’acronyme VISC, dont la définition est la réponse directe à la question suivante : lors de la génération des micro-instructions dans l’étape de décodage, ne peuvent-elles pas fonctionner ? en parallèle avec plusieurs cœurs à la place de le faire en un seul idem ?

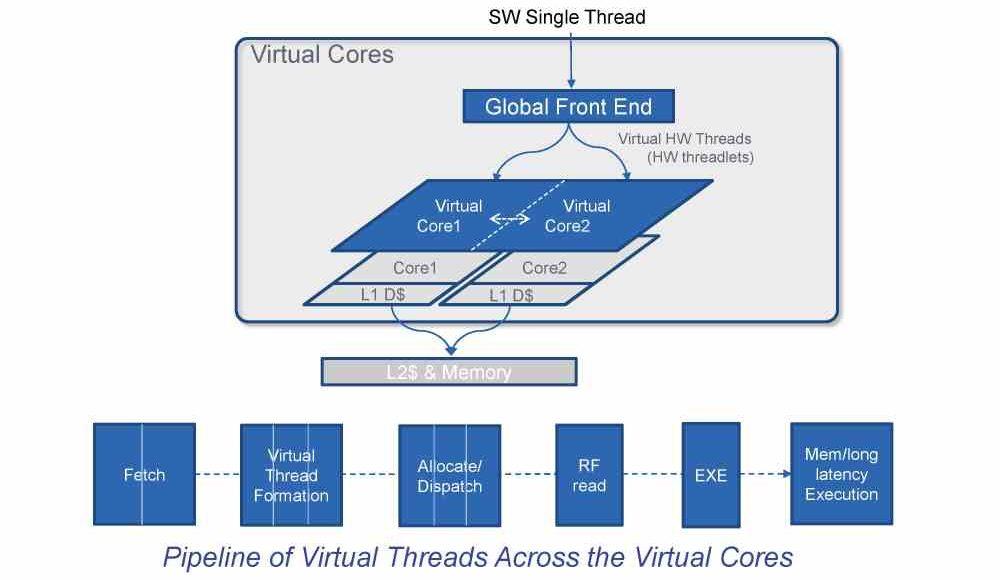

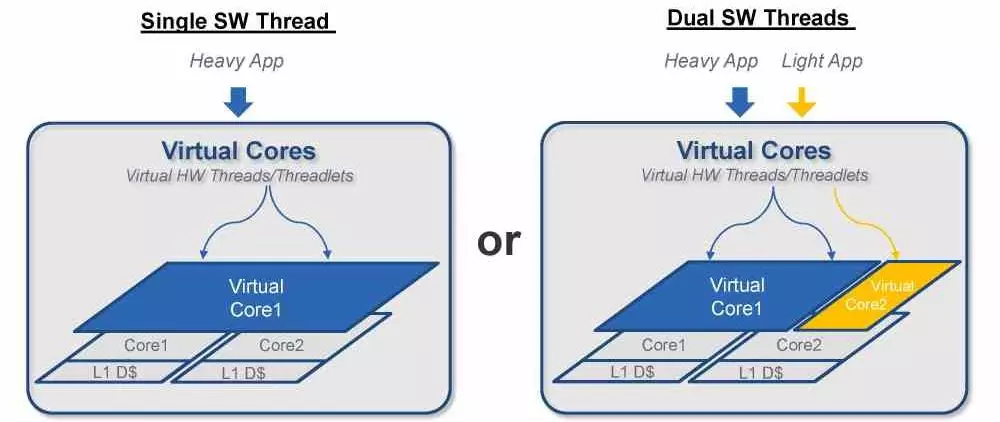

Eh bien, la réponse à la question sur l’architecture VISC, qui a été soulevée pour la première fois par une société appelée Soft Machines en 2015 en tant que concept pour améliorer les performances du processeur. Cette petite startup a été rachetée par Intel en 2016 et depuis lors, ils travaillent au développement d’une architecture VISC. Comment ça marche? Et bien, cela se définit très facilement : un seul thread d’exécution est envoyé au Global Front End du processeur, qui est converti en plusieurs qui remplissent la même fonction et qui fonctionnent en parallèle et tournent dans des cœurs virtuels. Le processus de conversion est exécuté au niveau logiciel via une couche de traduction, mais nous devons garder à l’esprit que cela peut être quelque chose d’aussi simple qu’un microcontrôleur effectuant le transfert des instructions.

Contrairement à ce qui se passe dans la répartition des tâches dans un processeur multicœur classique, dans une architecture VISC, il n’est pas prévu qu’un cœur soit libre de pouvoir exécuter une instruction, mais que les éléments pour l’exécuter soient disponibles au sein du processeur pour exécuter ce. Par exemple, il peut arriver que dans un noyau conventionnel l’unité vectorielle ne soit pas utilisée, mais sous ce paradigme, elle peut être utilisée pour former l’une des instructions.

VISC et performances

Lors de l’adoption d’un nouveau paradigme en termes d’architecture, la première chose à considérer est son impact sur les performances, car cela ne vaut pas la peine de changer le paradigme actuel si cela n’entraîne pas une augmentation des performances globales du processeur. La façon la plus classique d’augmenter les performances d’un processeur est d’augmenter le nombre d’instructions qui sont résolues par cycle d’horloge, cela signifie rendre le matériel de plus en plus complexe, du fait que l’ajout des cœurs nous devons compter toute l’infrastructure qui les entoure qui devient le même ou plus complexe.

Ce qui différencie VISC du reste n’est autre que la répartition des ressources processeur pour que l’exécution des différentes instructions s’effectue en quelques cycles d’horloge, entre 1 et 4 cœurs. De cette façon, s’il y a deux instructions en compétition pour d’autres ressources dans un cœur, alors elles peuvent être réaffectées très rapidement à une autre partie du processeur où ces mêmes ressources sont disponibles.

Le paradigme actuel, qui est l’exécution dans le désordre, consiste à réordonner l’exécution des instructions en fonction des ressources libres à tout moment, puis à réordonner la sortie des données déjà traitées. La limite ? L’allocation des ressources est effectuée au niveau monocœur plutôt qu’au niveau multicœur, et c’est la clé de meilleures performances pour les architectures VISC.

Ces processeurs existent-ils aujourd’hui ?

Bien que le concept soit très bon sur le papier, personne n’a encore présenté un processeur qui fonctionne sous ce paradigme, mais étant donné que nous approchons progressivement des limites du paradigme actuel, il est important de garder à l’esprit qu’il existe des solutions qui peuvent servir pour améliorer les performances CPU de nos PC pour l’avenir.

Disposer d’un processeur plus puissant, ce n’est pas seulement en avoir un plus rapide ou avec plus de cœurs, mais il s’agit de savoir tirer parti des ressources disponibles. L’exécution dans le désordre était la première étape dans ce sens, mais depuis lors, en dehors du passage au multicœur, les changements ont été généralement mineurs. VISC est encore un concept, mais ce n’est pas impossible et c’est un moyen de tirer parti des ressources disponibles dans le processeur de manière beaucoup plus efficace.

Jusqu’à présent, nous savons que le concept est possible dans un processeur puisque Soft Machines en a conçu et construit un avec ce paradigme, donc bien que ce soit à un niveau expérimental, nous savons qu’il est possible de réaliser une telle conception. Une autre chose différente est la difficulté d’amener l’ensemble des instructions et des registres x86 à ce paradigme, qui est extrêmement complexe par sa nature.