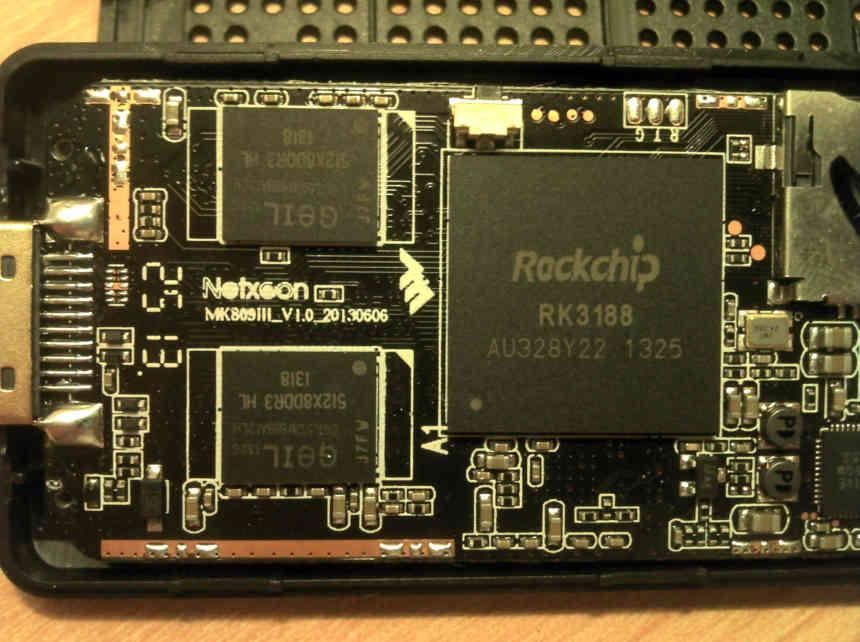

Bien qu’ils soient utilisés dans différents appareils, pour différentes applications, ils exécutent différents binaires et il y a des points qui les différencient, tous les SoC ont une architecture commune, ce qui affecte leurs performances et leur nature dans son ensemble.

Qu’est-ce qu’un SoC?

De nos jours, chaque processeur est un SoC, mais nous appelons SoC ceux qui rassemblent un CPU et un GPU dans le même espace, pour les différencier de ces SoC qui ne servent que de processeurs centraux ou de puces graphiques qui sont encore appelés respectivement CPU et GPU.

Les SoC se retrouvent aujourd’hui dans tous les types d’ordinateurs et présentent l’avantage économique de combiner plusieurs composants sur une seule puce. La raison en est que dans le processus, non seulement la fabrication de plusieurs puces est économisée en la simplifiant en une seule, mais également les tests correspondants.

Les SoC ne sont donc rien de plus qu’un produit de l’intégration continue des composants grâce à la loi de Moore, dans laquelle petit à petit le nombre de composants sur les cartes mères a été réduit au fur et à mesure de leur intégration les uns aux autres. Une telle intégration, cependant, comporte un certain nombre de compromis qui affectent ses performances et font qu’une conception basée sur un SoC a moins de performances en utilisant une puce séparée.

Architecture générale d’un SoC

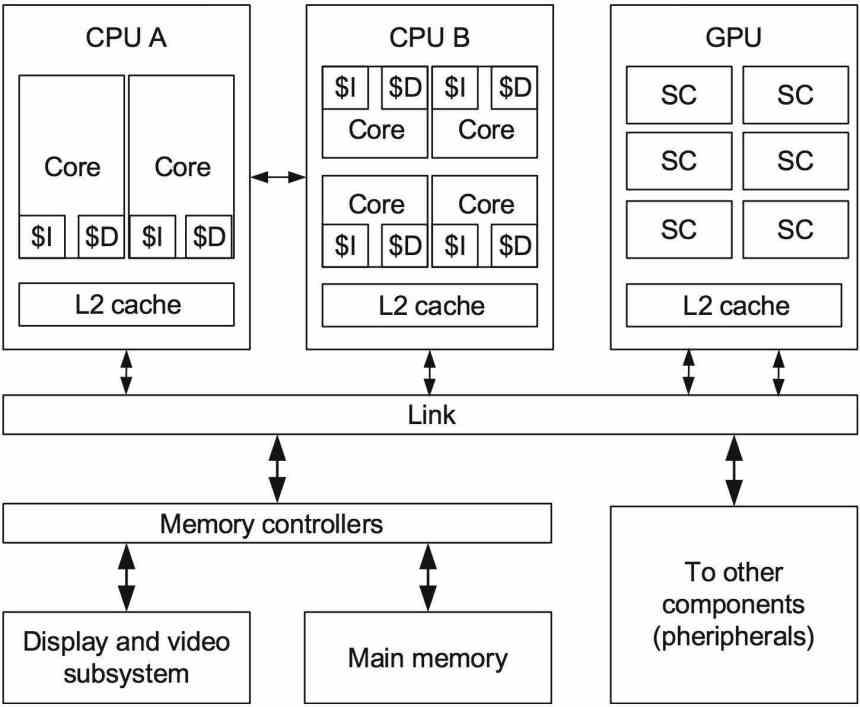

Quel que soit le type de SoC dont nous parlons, tous ont une série d’éléments en commun en ce qui concerne leur organisation. Que voulons-nous dire par là? L’organisation ou l’architecture est la manière dont les composants d’un processeur sont interconnectés les uns avec les autres au sein d’une puce intégrée.

Dans les SoC, tous les éléments partagent un accès commun à la même mémoire, cela signifie que dans tous les SoC, l’accès à la mémoire se fait via un seul composant. Ce qui est dans toutes les architectures le Northbridge ou north bridge, qui communique tous les composants du CPU entre eux et avec la mémoire RAM.

Le Northbridge n’exécute pas vraiment de programmes, mais il organise l’envoi et la réception des données, donc en interne, le SoC traite une grande quantité de données en continu et est la partie la plus importante lors de la conception d’un SoC.

Il existe un mythe parmi les utilisateurs selon lequel la création d’un SoC consiste à coller les différentes pièces ensemble. La réalité est très différente puisque l’interconnexion entre les composants nécessite la construction d’une infrastructure d’intercommunication spécifique et différente pour chaque SoC.

Architecture dans un SoC et accès mémoire

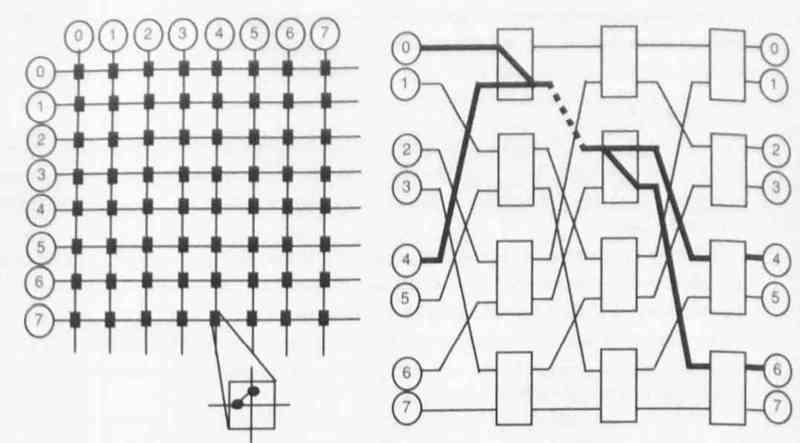

Dans le SoC, tous les composants partagent l’accès à la mémoire RAM, cela suppose des problèmes de contention. Qu’est-ce qu’un problème de confinement? C’est lorsque les demandes de mémoire sont si élevées que cela finit par ajouter plus de latence que la normale et ainsi rendre les performances de chaque élément du SoC pires qu’avec chaque élément ayant son propre type de mémoire.

La meilleure façon de remédier à cela est d’utiliser plusieurs canaux de mémoire en même temps, la chose habituelle est que dans les PC deux canaux de mémoire sont utilisés par SoC, dans les postes de travail 4 et dans les serveurs 8. Chaque canal de mémoire peut être utilisé par un composant matériel en même temps, mais en raison du grand nombre d’éléments accédant en même temps, cela ne suffit pas.

De plus, la gestion d’une interface mémoire multicanal complique davantage le Northbridge et augmente ainsi la taille de son SoC. C’est pourquoi ce sont les SoC pour serveurs qui ont la plus grande taille, non seulement en raison d’un plus grand nombre de cœurs, mais parce que l’espace plus grand pour le Northbridge leur permet d’ajouter plus de complexité face aux interfaces mémoire.

Mémoire cohérente versus mémoire non cohérente

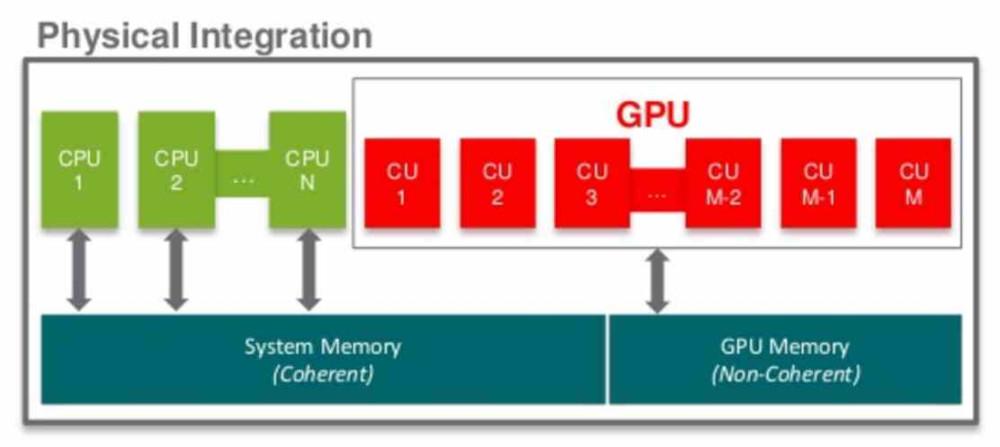

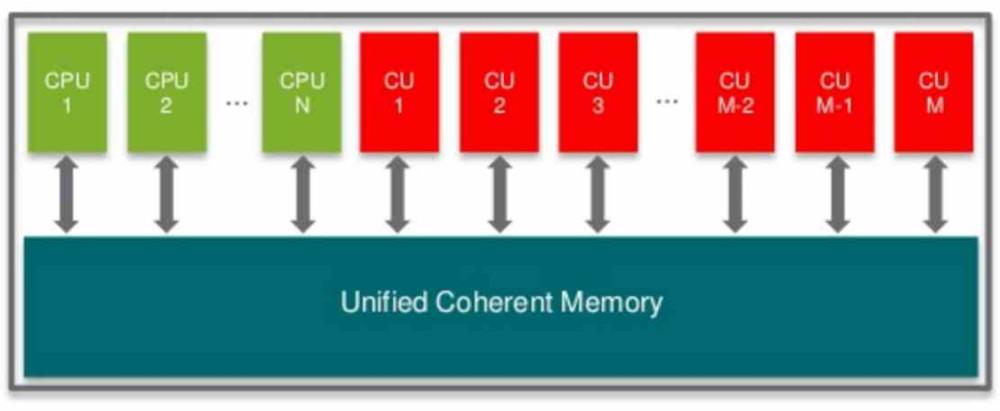

Dans un SoC, bien que l’accès à la mémoire soit unifié au niveau physique, il ne l’est pas au niveau de l’adressage. Lorsque nous disons qu’un composant du SoC est cohérent en termes de mémoire, nous voulons dire qu’ils pointent tous vers les mêmes adresses mémoire et lorsqu’un changement est effectué dans chaque partie de la mémoire RAM, le reste des éléments en est conscient.

La cohérence se produit en ce qui concerne le processeur, mais il existe des composants dans le SoC qui peuvent fonctionner sans mécanisme de cohérence. Cela oblige, en ce qui concerne la mémoire externe, une partie est affectée à la partie cohérente et d’autres aux parties non cohérentes. Lorsque le Northbridge du SoC reçoit une demande de mémoire dans un SoC qui a les deux types, il divise l’adressage de la mémoire, de manière à ce que les composants cohérents avec le CPU accèdent à une partie de la mémoire et à d’autres à une autre partie. de la mémoire.

La meilleure façon d’atteindre la cohérence de la mémoire est d’ajouter un niveau de cache supplémentaire, qui ne se trouve pas dans chacun des composants mais dans le Northbridge, où ils communiquent tous en commun. Cette méthode est courante parmi les SoC de smartphone et est la plus simple à mettre en œuvre pour assurer la cohérence de la mémoire.

Noyade thermique dans les SoC

Un autre problème des SoC est le fait que les composants sont très proches les uns des autres, ce qui signifie qu’ils peuvent atteindre moins de température que s’ils étaient montés en tant que composants séparés. Cela signifie que les vitesses d’horloge que chaque composant peut atteindre sont inférieures à séparément, ce qui affecte les performances.

Donc, dans un SoC, si vous voulez qu’un composant atteigne la vitesse maximale, il le fait parjure du reste des composants. Même sur les SoC avec des processeurs multicœurs, cela se produit entre différents cœurs, où certaines conceptions permettent à un seul cœur de fonctionner plus rapidement que les autres.

C’est aussi pourquoi de nombreux SoC ont la possibilité de connecter et de déconnecter différentes parties du GPU lorsqu’ils ne sont pas utilisés, mais cela doit être implémenté dans l’architecture du SoC lui-même et donc dans sa conception.