Le mot chiplet nous paraissait ridicule il y a quelques années, mais aujourd’hui c’est devenu un avenir sûr. Notamment du fait qu’il entraîne une réduction des coûts et rompt avec les limitations du système monolithique en termes de coût et d’encombrement. Il est donc tout à fait normal que l’industrie finisse par développer un connecteur universel entre chiplets qu’elle a baptisé UCIe.

Avec l’augmentation des coûts de production des processeurs, l’adoption de chiplets pour construire avec plusieurs puces ce qui se faisait auparavant avec une seule est une réalité. Au niveau PC, chacun des grands concepteurs de matériel a déjà lancé ou vient de lancer une architecture construite de cette manière. Il fallait donc tôt ou tard s’entendre sur la création d’un connecteur universel qui permettrait aux chiplets des différentes marques de communiquer entre elles.

L’industrie lance Universal Chiplet Interconnect Express

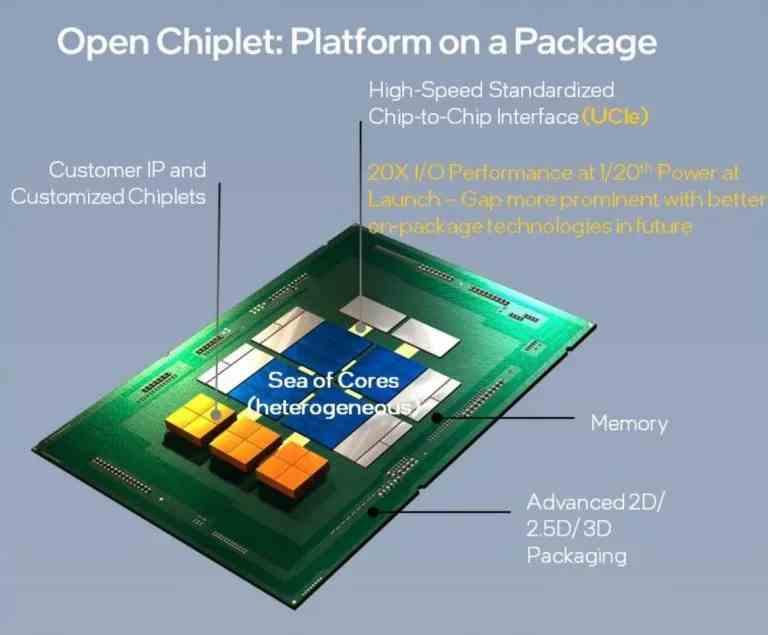

Les trois plus grandes fonderies du monde (TSMC, Intel et Samsung) ainsi qu’une série de partenaires technologiques tels que ARM, Google, Meta, Microsoft et Qualcomm ont lancé une nouvelle norme. Qui consiste en une interface de communication qu’ils ont baptisée UCIe ou Universal Chiplet Interconnect Express. Qui sert à faire communiquer entre elles les différentes puces montées sur un substrat commun. C’est-à-dire qu’un processeur qui, au lieu d’être composé d’une seule pièce, est composé de plusieurs qui sont interconnectés les uns avec les autres.

La nouvelle norme UCIe sIl est basé sur PCI Express avec Compute Express Link et entre autres, il permettra la création de chiplets constitués de pièces d’un seul fabricant, sinon que l’on pourra voir des architectures où non seulement des éléments avec des procédés de fabrication différents sont combinés, mais aussi de différents fournisseurs. Ce qui change complètement le paradigme actuel, puisque jusqu’à présent les solutions de ce type ont tendance à se focaliser sur les solutions d’un même constructeur car il n’existe pas de standard universel à ce jour.

En tout cas, l’existence de la nouvelle norme n’est pas quelque chose qui devrait nous surprendre, d’autant plus que les collaborations entre fonderies pour la création de différentes parties d’un même CPU, GPU ou APU seront de plus en plus courantes. Nous en avons le parfait exemple dans les collaborations entre Intel et TSMC pour les futurs projets du premier.

Quelles sont les caractéristiques de l’USI ?

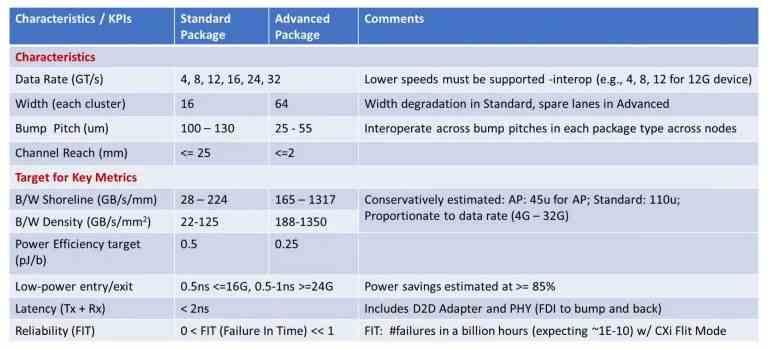

Pour le moment, la norme n’est pas définitive, mais ils ont publié une série de spécifications initiales sous la forme de la version 1.0 de la norme. Ce qui vient avec deux types d’interconnexions différents. N’oublions pas qu’il s’agit d’interconnexions verticales de chacun des chiplets par rapport à l’interposeur, qui est le substrat de communication sur lequel ils sont montés pour transmettre le signal et donc les données. Cela leur permet d’atteindre bandes passantes supérieures à un téraoctet par seconde à des niveaux de consommation allant jusqu’à 0,25 pJ par bit transmis.

Traduit en quelque chose qui peut être compris en langage conventionnel, il faut tenir compte du fait que la vitesse de transfert vers la RAM traditionnelle est actuellement généralement comprise entre 6 et 8 pJ/bit en moyenne, selon le type de mémoire utilisée. La faible consommation est l’une des clés de ce type d’interconnexions, conçues pour transmettre de grandes quantités de bande passante entre les différents composants. Ce qui est essentiel pour les processeurs composés de dizaines de cœurs sur le marché des serveurs, ainsi que pour les GPU composés de chiplets.