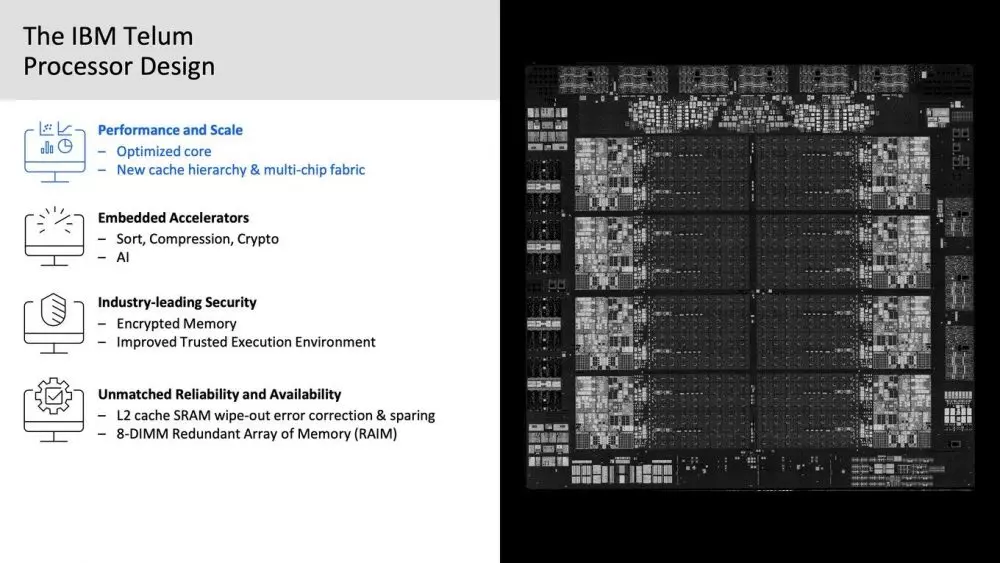

Il semble que, du moins pour IBM, l’avenir de l’informatique n’implique pas d’augmenter de plus en plus le nombre de cœurs de processeur, mais bien l’inverse ; Avec cette nouvelle génération de CPU, le constructeur a réduit le nombre de cœurs, mais en retour a considérablement amélioré d’autres aspects tels que doubler la quantité de cache L3 (256 Mo contre 128 Mo de son prédécesseur), soit en introduisant des cœurs séparés dédiés exclusivement à Intelligence artificielle.

Voici IBM Telum Z, l’avenir de l’informatique selon IBM

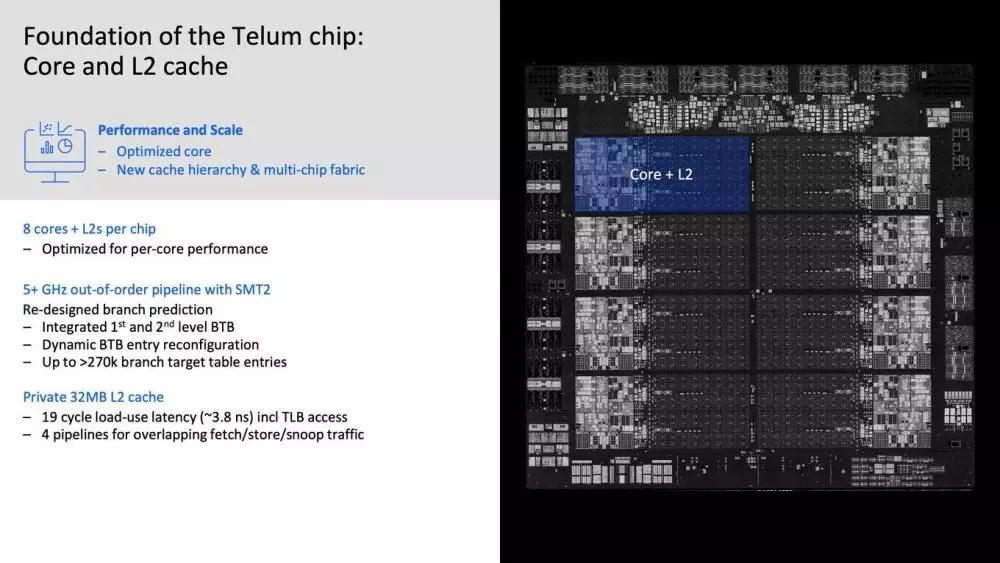

La partie droite de la diapositive que nous avons placée au-dessus de ces lignes indique clairement que la composition interne de la matrice a un total de 8 cœurs physiques, qui dans ce cas sont capables de générer 2 threads de processus par cœur grâce à la technologie IBM SMT2 (comme Intel HyperThreading ou AMD SMT) pour un total de 16 threads.

Une particularité de ce processeur est que tous ses cœurs sont hors service (hors service), et sont donc conçus pour exécuter des instructions en évitant les arrêts d’exécution et en augmentant ainsi le nombre moyen d’instructions qu’il est capable de résoudre par cycle d’horloge. La conception de ce processeur est donc destinée aux applications temps réel qui nécessitent une réponse instantanée du processeur, c’est pourquoi IBM s’est concentré sur maximiser les performances à un seul thread.

Pour cela, IBM a intégré 32 Mo de cache L2 qui est initialement exclusivement disponible pour chaque cœur CPU (4 Mo par cœur) et, comme nous l’avons dit précédemment, 256 Mo de cache L3. Comparativement, un processeur Intel Core i7-10700K ne dispose que de 20 Mo de ce qu’Intel appelle Smart Cache (L2 + L3), donc comme vous pouvez le voir, nous sommes confrontés à une énorme quantité de mémoire cache. De plus, IBM a fourni quatre pipelines qui communiquent avec les cœurs en seulement 19 cycles d’horloge (3,8 ns), donc travailler avec le cache devrait être extrêmement rapide.

Enfin, il convient de mentionner que ce processeur IBM est fabriqué par Samsung avec son nœud processus à 7 nm; Il compte 22 500 millions de transistors dans une surface de 530 mm² et, attention, il est construit en 17 couches. IBM n’a pas fourni plus de détails à ce sujet, mais nous resterons à l’écoute car c’est assez intéressant.

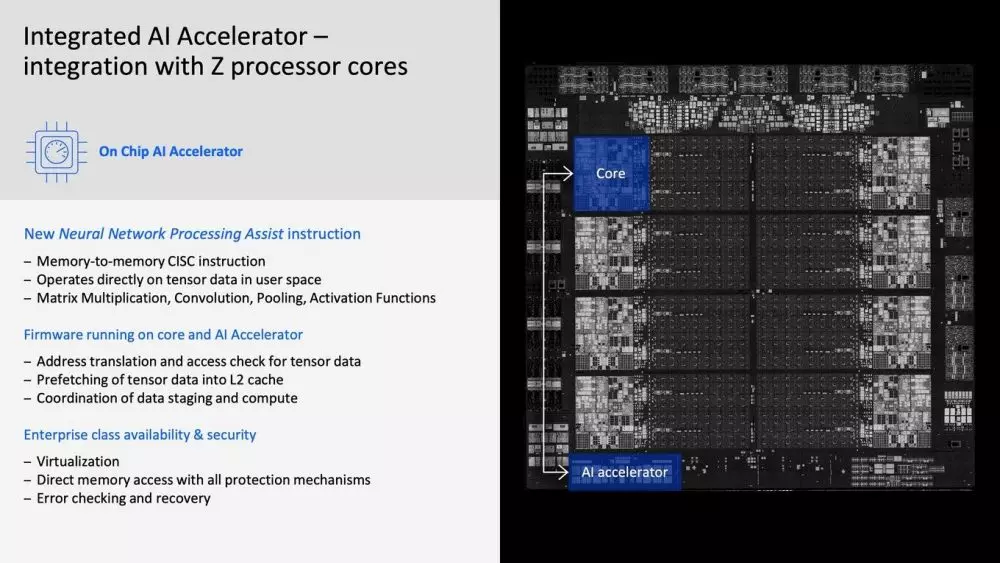

Cœurs exclusifs pour les applications d’Intelligence Artificielle

L’une des particularités qui rend ce processeur IBM Z Telum très intéressant est le fait qu’ils ont intégré noyaux spécifiques pour l’Intelligence Artificielle (C’est-à-dire que par rapport à la génération précédente, le nombre de cœurs a été réduit de 12 à 8 mais, en plus des améliorations dont nous avons déjà parlé, il a en fait plus de cœurs en les ayant avec des performances spécifiques).

Selon IBM, ces cœurs atteignent un débit de 6 TFLOPS dans les calculs FP16, et il convient de mentionner qu’il les traite littéralement comme des accélérateurs d’IA. Ces cœurs ont un accès direct au cache L2 des cœurs, de sorte que les données peuvent être lues à des vitesses de 120 Go/s et écrites à 80 Go/s ; Selon le constructeur, ces données peuvent être pré-traitées avant d’être disponibles dans l’accélérateur pour l’IA lui-même, augmentant la bande passante à 600 Go/s, un véritable scandale de pouvoir traiter les données quasi instantanément.

Bien sûr, bien qu’avant d’avoir comparé le cache de ce processeur IBM avec un processeur Intel grand public, il n’est pas conçu pour des applications grand public, encore moins mais pour des applications en temps réel telles que la finance, la bourse, l’assurance, la médecine, les infrastructures, etc. . . . On suppose en outre que ces processeurs sont conçus pour être intégrés dans des systèmes multi-puces, et selon IBM, ils peuvent même fonctionner dans une double matrice avec des racks de 8 à 32 processeurs.